参数资料

| 型号: | AD9548BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 107/112页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN/SYNCHRONIZR 88LFCSP |

| 产品变化通告: | AD9548 Mask Change 20/Oct/2010 |

| 标准包装: | 1 |

| 类型: | 时钟/频率发生器,同步器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 750kHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 88-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 88-LFCSP-VQ(12x12) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页当前第107页第108页第109页第110页第111页第112页

AD9548

Data Sheet

Rev. E | Page 94 of 112

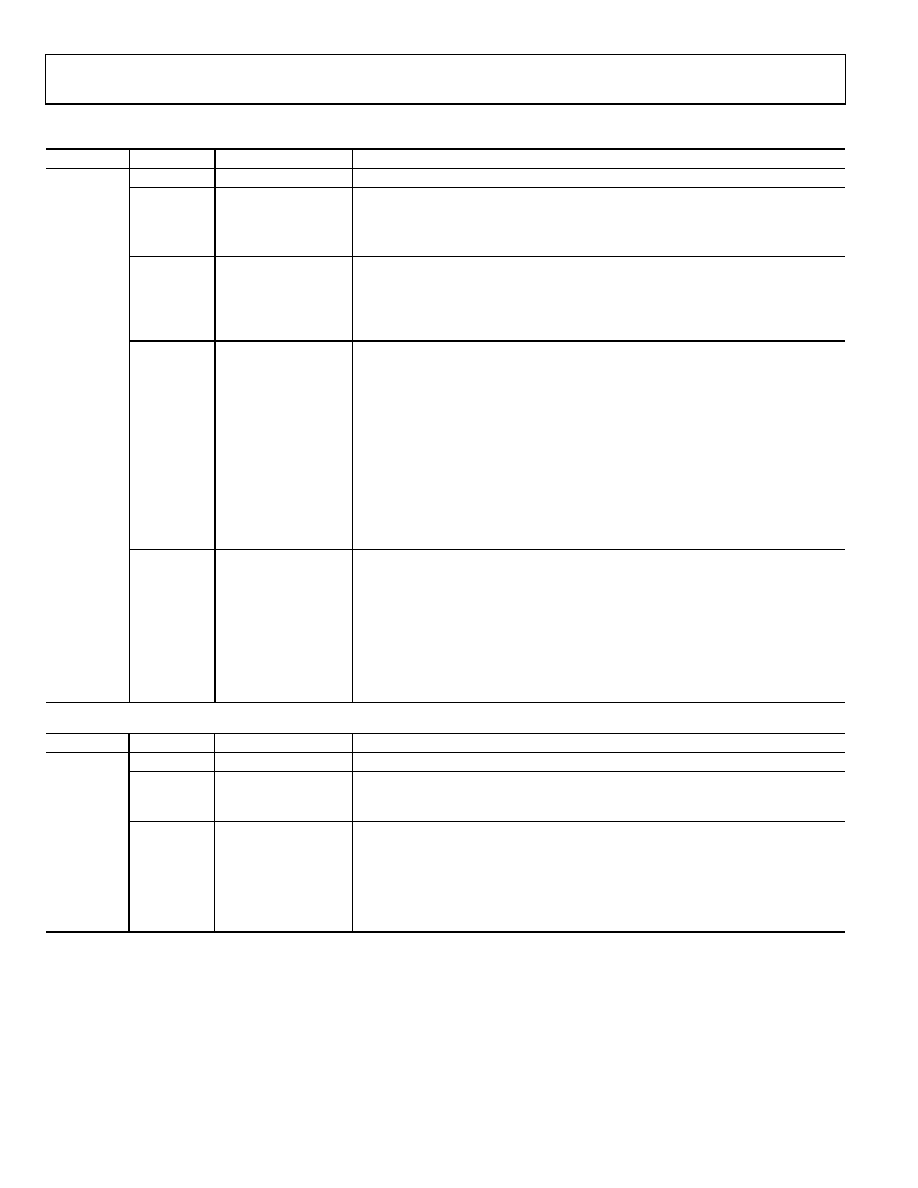

Table 120. Loop Mode

Address

Bits

Bit Name

Description

0x0A01

[7]

Unused

[6]

User holdover

Force the device into holdover mode.

0 (default) = normal operation.

1 = force device into holdover mode.

The device behaves as though all input references are faulted.

[5]

User freerun

Force the device into free-run mode.

0 (default) = normal operation.

1 = force device into free-run mode.

The free running frequency tuning word register specifies the DDS output frequency.

Note that, when the user freerun bit is set, it overrides the user holdover bit.

[4:3]

User selection mode

Select the operating mode of the reference switching state machine.

00 (default) = automatic mode. The fully automatic priority-based algorithm selects

the active reference (Bits[2:0] are ignored).

01 = fallback mode. The active reference is the user reference (Bits[2:0]) as long as it is

valid. Otherwise, use the fully automatic priority-based algorithm to select the active

reference.

10 = holdover mode. The active reference is the user reference (Bits[2:0]) as long as it

is valid. Otherwise, enter holdover mode.

11 = manual mode. The active reference is always the user reference (Bits[2:0]). When

using manual mode, be sure that the reference declared as the user reference

(Bits[2:0]) is programmed for manual reference-to-profile assignment in the

appropriate manual reference profile selection register (Address 0503 to Address

0506).

[2:0]

User reference

selection

Input reference when user selection mode = 01, 10, or 11.

000 (default) = Input Reference A

001 = Input Reference AA

010 = Input Reference B

011 = Input Reference BB

100 = Input Reference C

101 = Input Reference CC

110 = Input Reference D

111 = Input Reference DD

Table 121. Cal/Sync

Address

Bits

Bit Name

Description

0x0A02

[7:2]

unused

[1]

Sync distribution

Setting this bit (default = 0) initiates synchronization of the clock distribution output.

While this bit = 1, the clock distribution output stalls. Synchronization occurs on the

1 to 0 transition of this bit.

[0]

Calibrate system

clock

A 0 to 1 transition on this bit (default = 0), followed by an IO_UPDATE, initiates an

internal calibration of the SYSCLK PLL (assuming it is enabled). The calibration

routine automatically selects the proper VCO frequency band and signal amplitude.

The internal system clock stalls during the calibration procedure, disabling the

device until the calibration is complete (a few milliseconds). If the user wishes to

recalibrate the SYSCLK PLL and this bit is already set to 1, the user must first write a 0

to this bit, issue an IO_UPDATE, write a 1 to this bit, and issue another IO_UPDATE.

相关PDF资料 |

PDF描述 |

|---|---|

| V375C36M150BL3 | CONVERTER MOD DC/DC 36V 150W |

| MAX3676EHJ+ | IC CLOCK RECOVERY 32-TQFP |

| ADN2813ACPZ | IC CLK/DATA REC 1.25GBPS 48LFCSP |

| AD800-52BRZ | IC CLK\DATA RECOVERY PLL 20SOIC |

| SY87700VZH | IC CLK/DATA RECOVERY 3.3V 28SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9548BCPZ-REEL7 | 功能描述:IC CLOCK GEN/SYNCHRONIZR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| AD9548XCPZ | 制造商:Analog Devices 功能描述: |

| AD9549 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Input Network Clock Generator/Synchronizer |

| AD9549/PCBZ | 制造商:Analog Devices 功能描述:DUAL INPUT NETWORK CLOCK GEN/SYNCHRONIZER - Bulk |

| AD9549A/PCBZ | 功能描述:BOARD EVALUATION FOR AD9549A RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

发布紧急采购,3分钟左右您将得到回复。