参数资料

| 型号: | AD9558BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 104/104页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK TRANSLATOR 64LFCSP |

| 产品变化通告: | AD9558 Minor Metal Mask Change 17/Apr/2012 |

| 标准包装: | 1 |

| 类型: | 时钟/频率转换器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,HSTL,LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 4:6 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.25GHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页当前第104页

Data Sheet

AD9558

Rev. B | Page 99 of 104

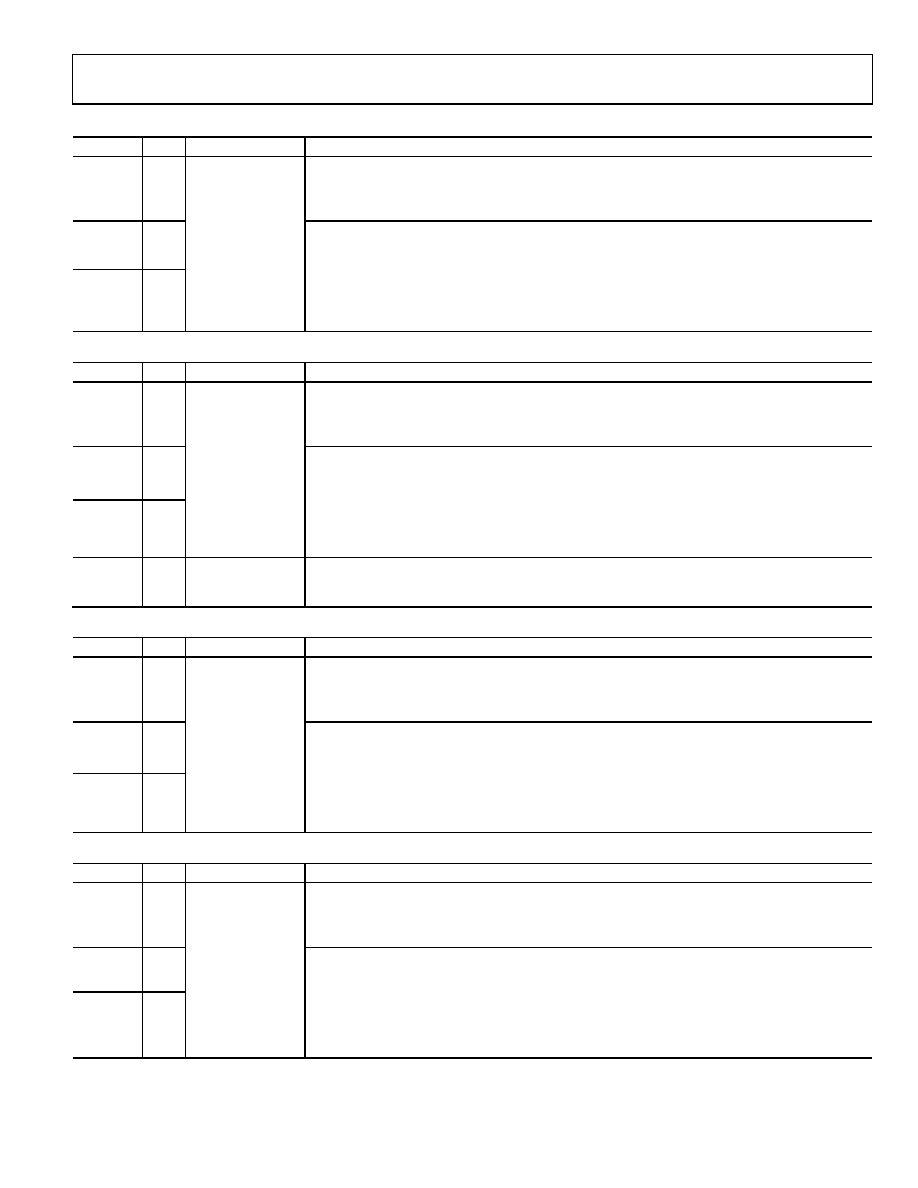

Table 117. EEPROM Storage Sequence for Output PLL Settings

Address

Bits

Bit Name

Description

0x0E1D

[7:0]

APLL

The default value of this register is 0x08, which the controller interprets as a data instruction. Its

decimal value is 8, which tells the controller to transfer nine bytes of data (8 + 1), beginning at the

address that is specified by the next two bytes. The controller stores 0x08 in the EEPROM and

increments the EEPROM address pointer.

0x0E1E

[7:0]

The default value of these two registers is 0x0400. Note that Register 0x0E1E and Register 0x0E1F

are the most significant and least significant bytes of the target address, respectively. Because the

previous register contains a data instruction, these two registers define a starting address (in this

case, 0x0400). The controller stores 0x0400 in the EEPROM and increments the EEPROM pointer by 2.

It then transfers nine bytes from the register map (beginning at Address 0x0400) to the EEPROM

and increments the EEPROM address pointer by 10 (nine data bytes and one checksum byte). The

nine bytes transferred correspond to APLL parameters in the register map.

0x0E1F

[7:0]

Table 118. EEPROM Storage Sequence for Clock Distribution Settings

Address

Bits

Bit Name

Description

0x0E20

[7:0]

Clock distribution

The default value of this register is 0x15, which the controller interprets as a data instruction. Its

decimal value is 21, which tells the controller to transfer 22 bytes of data (21+1), beginning at the

address that is specified by the next two bytes. The controller stores 0x15 in the EEPROM and

increments the EEPROM address pointer.

0x0E21

[7:0]

The default value of these two registers is 0x0500. Note that Register 0x0E21 and Register 0x0E22

are the most significant and least significant bytes of the target address, respectively. Because the

previous register contains a data instruction, these two registers define a starting address (in this

case, 0x0500). The controller stores 0x0500 in the EEPROM and increments the EEPROM pointer by 2.

It then transfers 22 bytes from the register map (beginning at Address 0x0500) to the EEPROM and

increments the EEPROM address pointer by 23 (22 data bytes and one checksum byte). The

22 bytes transferred correspond to the clock distribution parameters in the register map.

0x0E22

[7:0]

0x0E23

[7:0]

I/O update

The default value of this register is 0x80, which the controller interprets as an I/O update

instruction. The controller stores 0x80 in the EEPROM and increments the EEPROM address

pointer.

Table 119. EEPROM Storage Sequence for Reference Input Settings

Address

Bits

Bit Name

Description

0x0E24

[7:0]

Reference inputs

The default value of this register is 0x03, which the controller interprets as a data instruction. Its

decimal value is 3, so this tells the controller to transfer four bytes of data (3 + 1), beginning at the

address that is specified by the next two bytes. The controller stores 0x03 in the EEPROM and

increments the EEPROM address pointer.

0x0E25

[7:0]

The default value of these two registers is 0x0600. Note that Register 0x0E25 and Register 0x0E26

are the most significant and least significant bytes of the target address, respectively. Because the

previous register contains a data instruction, these two registers define a starting address (in this

case, 0x0600). The controller stores 0x0600 in the EEPROM and increments the EEPROM pointer by 2.

It then transfers four bytes from the register map (beginning at Address 0x0600) to the EEPROM

and increments the EEPROM address pointer by 5 (four data bytes and one checksum byte). The

four bytes that are transferred correspond to the reference inputs parameters in the register map.

0x0E26

[7:0]

Table 120. EEPROM Storage Sequence for Frame Sync Settings

Address

Bit

Bit Name

Description

0x0E27

[7:0]

Frame sync

The default value of this register is 0x01, which the controller interprets as a data instruction. Its

decimal value is 1, which tells the controller to transfer two bytes of data (1 + 1), beginning at the

address specified by the next two bytes. The controller stores 0x01 in the EEPROM and increments

the EEPROM address pointer.

0x0E28

[7:0]

The default value of these two registers is 0x0640. Note that Register 0x0E28 and Register 0x0E29

are the most significant and least significant bytes of the target address, respectively. Because the

previous register contains a data instruction, these two registers define a starting address (in this

case, 0x0640). The controller stores 0x0640 in the EEPROM and increments the EEPROM pointer by 2.

It then transfers two bytes from the register map (beginning at Address 0x0640) to the EEPROM

and increments the EEPROM address pointer by 3 (two data bytes and one checksum byte). The

two bytes transferred correspond to the reference inputs parameters in the register map.

0x0E29

[7:0]

相关PDF资料 |

PDF描述 |

|---|---|

| AD9557BCPZ | IC CLOCK TRANSLATOR 40LFCSP |

| V375C36M150BG | CONVERTER MOD DC/DC 36V 150W |

| AD9547BCPZ | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| D38999/20MF11JN | CONN RCPT 11POS WALL MNT W/SCKT |

| AD9549ABCPZ | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9558BCPZ-REEL7 | 功能描述:IC CLK XLATR PLL 1250MHZ 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| AD9559 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual PLL, Quad Input, Multiservice Line Card Adaptive Clock Translator |

| AD9559/PCBZ | 功能描述:时钟和定时器开发工具 Multi-protocol line card dual clock RoHS:否 制造商:Texas Instruments 产品:Evaluation Modules 类型:Clock Conditioners 工具用于评估:LMK04100B 频率:122.8 MHz 工作电源电压:3.3 V |

| AD9559BCPZ | 功能描述:时钟发生器及支持产品 Multi-protocol line card dual clock RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| AD9559BCPZ-REEL7 | 功能描述:时钟发生器及支持产品 Multi-protocol line card dual clock RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。