- 您现在的位置:买卖IC网 > PDF目录17103 > AD9785-DPG2-EBZ (Analog Devices Inc)BOARD EVALUATION FOR AD9785 PDF资料下载

参数资料

| 型号: | AD9785-DPG2-EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 21/64页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD9785 |

| 标准包装: | 1 |

| 系列: | TxDAC® |

| DAC 的数量: | 2 |

| 位数: | 12 |

| 采样率(每秒): | 800M |

| 数据接口: | 串行 |

| 设置时间: | 22ms |

| DAC 型: | 电流 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板,缆线,CD |

| 已用 IC / 零件: | AD9785 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

AD9785/AD9787/AD9788

Rev. A | Page 28 of 64

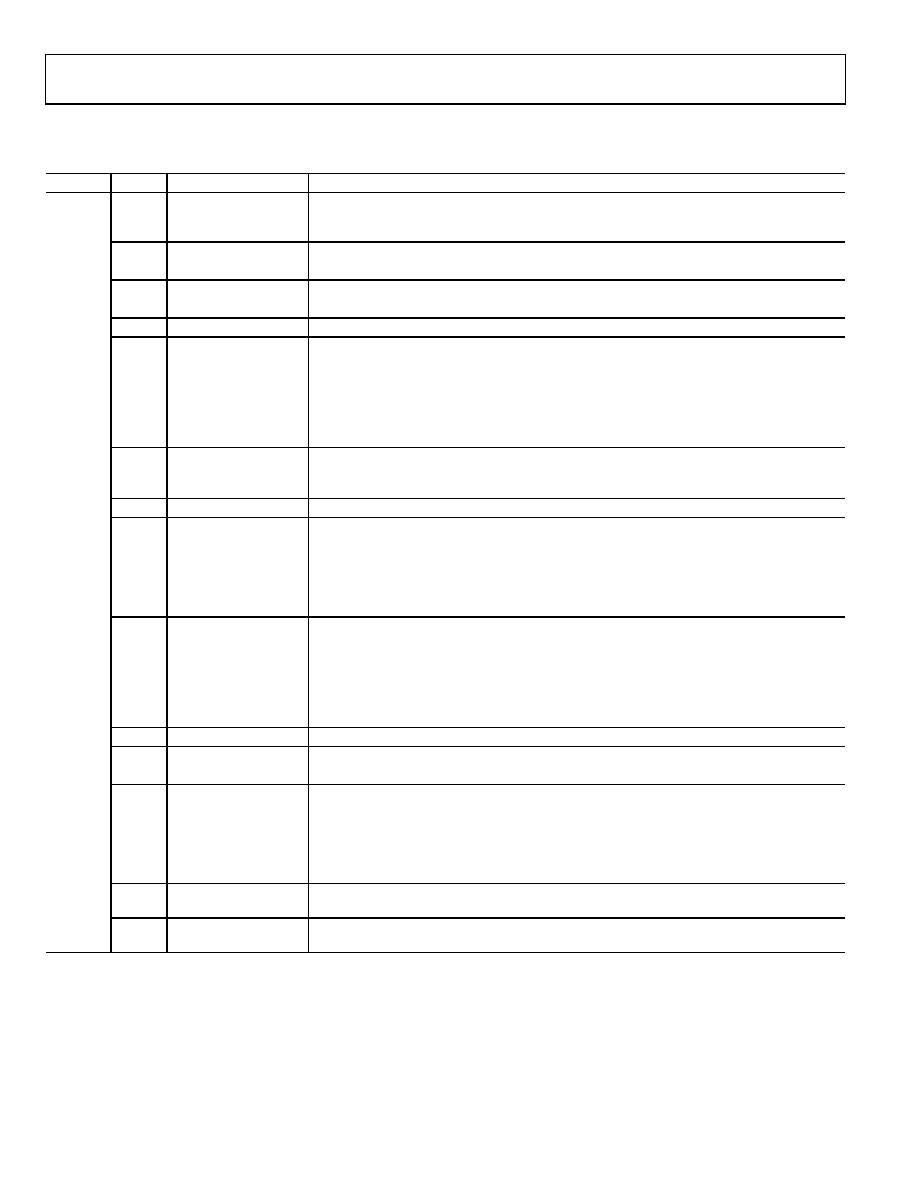

The multichip synchronization register (MSCR) comprises four bytes located at Address 0x03.

Table 13. Multichip Synchronization Register (MSCR)

Address

Bit

Name

Description

0x03

[31:27]

Correlate Threshold

[4:0]

Sets the threshold for determining if the received synchronization data can be demodulated

accurately. A smaller threshold value makes the demodulator more noise immune; however,

the system becomes more susceptible to false locks (or demodulation errors).

[26]

SYNC_I enable

0: Default. The synchronization receive logic is disabled.

1: The synchronization receive logic is enabled.

[25]

SYNC_O enable

0: Default. The output synchronization pulse generation logic is disabled.

1: The output synchronization pulse generation logic is enabled.

[24]

Set low

This bit should always be set low.

[23:19]

SYNC_I Delay [4:0]

This value programs the value of the delay line of the SYNC_I signal. The delay line resolution

is 80 ps per step.

00000: nominal delay

00001: adds 80 ps delay to SYNC_I

00010: adds 160 ps delay to SYNC_I

…

11111: adds 2480 ps delay to SYNC_I

[18]

Sync error check mode

Specifies the synchronization pulse error check mode.

0: Manual error check

1: Automatic continuous error check

[17]

Set low

This bit should always be set low.

[16]

DATACLK input

0: Default. Slave mode is disabled.

1: Slave mode is enabled. Pin 37 functions as an input for the DATACLK signal, called DCI

(DATACLK input) in this mode. Depending on the state of Bit 1 in the DSCR register (Address

0x02), the sampling edge (where the data is latched into the AD9785/AD9787/AD9788) can

be programmed to be aligned with either the rising or falling edge of DCI. This mode can

only be used with 4× or 8× interpolation.

[15:11]

SYNC_O Delay [4:0]

This value programs the value of the delay line of the SYNC_O signal. The delay of SYNC_O is

relative to REFCLK. The delay line resolution is 80 ps per step.

00000: nominal delay

00001: adds 80 ps delay to SYNC_O

00010: adds 160 ps delay to SYNC_O

…

11111: adds 2480 ps delay to SYNC_O

[10]

Set high

This bit should always be set high.

[9]

SYNC_O polarity

0: Default. SYNC_O changes state on the rising edge of DACCLK.

1: SYNC_O is generated on the falling edge of DACCLK.

[8]

Sync loopback enable

0: Default. The AD9785/AD9787/AD9788 are not operating in internal loopback mode.

1: If the SYNC_O enable and Sync loopback enable bits are set, the AD9785/AD9787/AD9788

are operating in a mode in which the internal synchronization pulse of the device is used at

the multichip receiver logic and the SYNC_I+ and SYNC_I input pins are ignored. For proper

operation of the loopback synchronization mode, the synchronization driver enable and

sync enable bits must be set.

[7:4]

Clock State [3:0]

This value determines the state of the internal clock generation state machine upon

synchronization.

[3:0]

Sync Timing Margin

[3:0]

These bits are the synchronization window delay word. These bits are don’t care if the

synchronization driver enable bit is cleared.

相关PDF资料 |

PDF描述 |

|---|---|

| EEM36DTMD-S189 | CONN EDGECARD 72POS R/A .156 SLD |

| EEM36DTMH-S189 | CONN EDGECARD 72POS R/A .156 SLD |

| 0210390421 | CABLE FLAT FLEX 1.18" 1MM 26POS |

| EVAL-AD5791SDZ | BOARD EVAL FOR AD5791 |

| VE-J2R-EZ | CONVERTER MOD DC/DC 7.5V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9785-EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For AD9785 制造商:Analog Devices 功能描述:DUAL 12B, 1GSPS D-A CONVERTER - Bulk 制造商:Analog Devices 功能描述:Digital to Analog Eval. Board |

| AD9786 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 200 MSPS/500 MSPS TxDAC+ with 2】/4】/8】 Interpolation and Signal Processing |

| AD9786BSV | 制造商:Analog Devices 功能描述:DAC 1-CH Interpolation Filter 16-bit 80-Pin TQFP EP 制造商:Analog Devices 功能描述:IC 16BIT DAC SMD 9786 TQFP80 |

| AD9786BSVRL | 制造商:Analog Devices 功能描述:DAC 1-CH Interpolation Filter 16-bit 80-Pin TQFP EP T/R |

| AD9786BSVZ | 功能描述:IC DAC 16BIT INTERPOL/SP 80TQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC+® 标准包装:1 系列:- 设置时间:4.5µs 位数:12 数据接口:串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOICN 包装:剪切带 (CT) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):* 其它名称:MCP4921T-E/SNCTMCP4921T-E/SNRCTMCP4921T-E/SNRCT-ND |

发布紧急采购,3分钟左右您将得到回复。