- 您现在的位置:买卖IC网 > PDF目录19382 > ADSP-21161NCCAZ100 (Analog Devices Inc)IC DSP CONTROLLER 32BIT 225MBGA PDF资料下载

参数资料

| 型号: | ADSP-21161NCCAZ100 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 34/60页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 32BIT 225MBGA |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | 主机接口,连接端口,串行端口 |

| 时钟速率: | 100MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 128kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.80V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 225-BGA,CSPBGA |

| 供应商设备封装: | 225-CSPBGA(17x17) |

| 包装: | 托盘 |

| 其它名称: | ADSP21161NCCAZ100 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

Rev. C

|

Page 4 of 60

|

January 2013

When using the DAGs to transfer data in SIMD mode, two data

values are transferred with each access of memory or the regis-

ter file.

SIMD is supported only for internal memory accesses and is not

supported for off-chip accesses.

Independent, Parallel Computation Units

Within each processing element is a set of computational units.

The computational units consist of an arithmetic/logic unit

(ALU), multiplier, and shifter. These units perform single-cycle

instructions. The three units within each processing element are

arranged in parallel, maximizing computational throughput.

Single multifunction instructions execute parallel ALU and

multiplier operations. In SIMD mode, the parallel ALU and

multiplier operations occur in both processing elements. These

computation units support IEEE 32-bit single-precision float-

ing-point, 40-bit extended precision floating-point, and 32-bit

fixed-point data formats.

Data Register File

A general-purpose data register file is contained in each pro-

cessing element. The register files transfer data between the

computation units and the data buses, and store intermediate

results. These 10-port, 32-register (16 primary, 16 secondary)

register files, combined with the SHARC enhanced Harvard

architecture, allow unconstrained data flow between computa-

tion units and internal memory. The registers in PEX are

referred to as R0–R15 and in PEY as S0–S15.

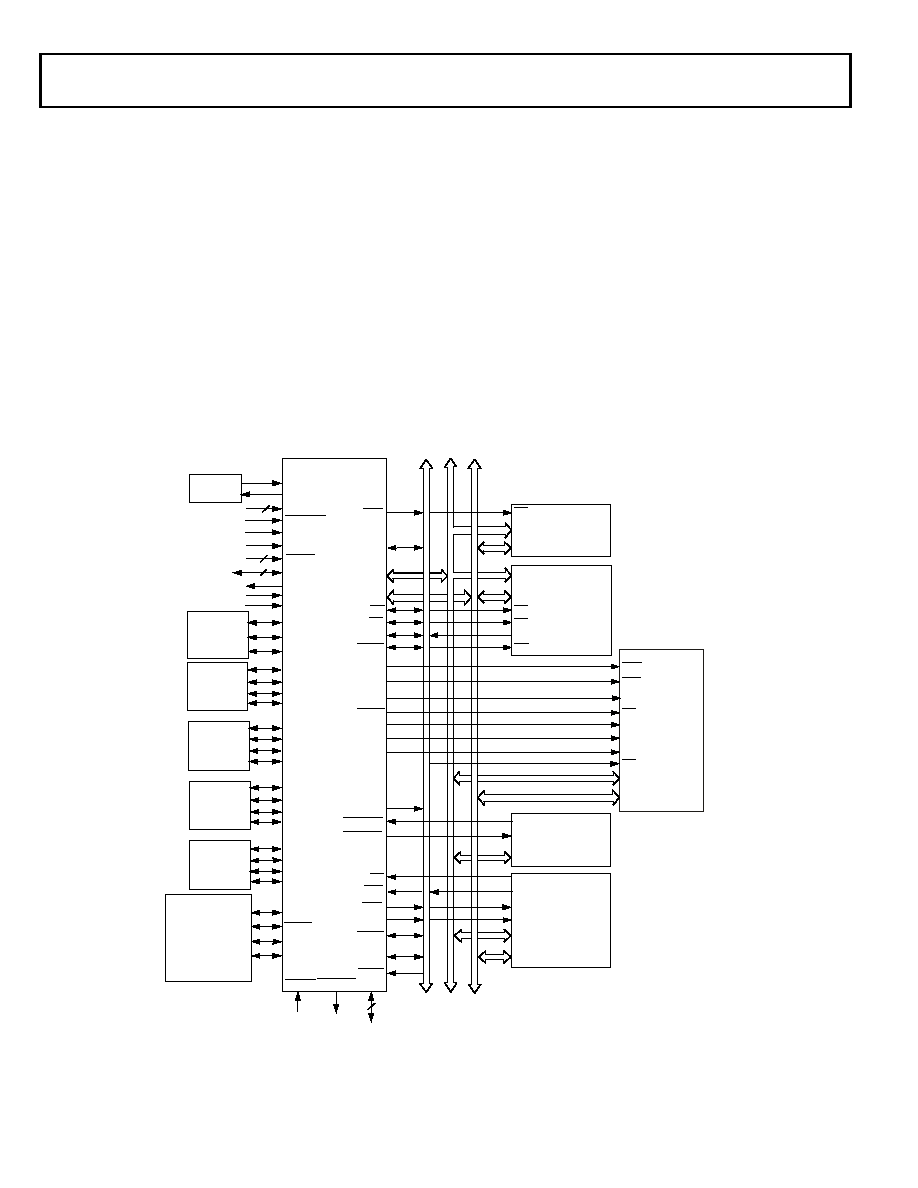

Single-Cycle Fetch of Instruction and Four Operands

The ADSP-21161N features an enhanced Harvard architecture

in which the data memory (DM) bus transfers data and the pro-

gram memory (PM) bus transfers both instructions and data

(see Figure 2). With the ADSP-21161N’s separate program and

data memory buses and on-chip instruction cache, the proces-

sor can simultaneously fetch four operands (two over each data

bus) and an instruction (from the cache), all in a single cycle.

Figure 2. System Diagram

DMA DEVICE

(OPTIONAL)

DATA

CLKOUT

DMAR2-1

DMAG2-1

ADDR

DATA

HOST

PROCESSOR

INTERFACE

(OPTIONAL)

3

12

CLOCK

CLKIN

XTAL

IRQ2-0

2

CLK_CFG1-0

EBOOT

LBOOT

FLAG11-0

TIMEXP

CLKDBL

RESET

JTAG

7

SBTS

ADSP-21161N

BMS

LINK

DEVICES

(2 MAX)

(OPTIONAL)

LXCLK

LXACK

LXDAT7-0

SCLK0

D0B

D0A

FS0

SERIAL

DEVICE

(OPTIONAL)

CS

BOOT

EPROM

(OPTIONAL)

ADDR

MEMORY

AND

PERIPHERALS

(OPTIONAL)

OE

DATA

CS

RD

RAS

ACK

BR6-1

RPBA

ID2-0

PA

HBG

HBR

SDWE

MS3-0

WR

DATA47-16

DATA

ADDR

CS

ACK

WE

ADDR23-0

D

A

T

A

C

O

N

T

R

O

L

A

D

R

E

S

BRST

SDRAM

(OPTIONAL)

SCLK1

D1B

D1A

FS1

SERIAL

DEVICE

(OPTIONAL)

SCLK2

D2B

D2A

FS2

SERIAL

DEVICE

(OPTIONAL)

SCLK3

D3B

D3A

FS3

SERIAL

DEVICE

(OPTIONAL)

SPICLK

MISO

MOSI

SPIDS

SPI

COMPATIBLE

DEVICE

(HOSTOR SLAVE)

(OPTIONAL)

DATA

CAS

RAS

DQM

WE

ADDR

CS

A10

CKE

CLK

DQM

CAS

REDY

SDCKE

SDA10

SDCLK1-0

RSTOUT

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B1V-CV-F1 | CONVERTER MOD DC/DC 5.8V 150W |

| THJD107M010RJN | CAP TANT 100UF 10V 20% 2917 |

| VI-2NZ-CY-F3 | CONVERTER MOD DC/DC 2V 20W |

| 2300973 | CONN 37POS D-SUB W/SCREW |

| 1130-681K-RC | CHOKE RF HI CURR 680UH 10% RAD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21161NKCA-100 | 功能描述:IC DSP CONTROLLER 32BIT 225MBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21161NKCA-100Z | 制造商:Analog Devices 功能描述: |

| ADSP-21161NKCAZ100 | 功能描述:IC DSP CONTROLLER 32BIT 225MBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21161NYCAZ110 | 功能描述:IC DSP CONTROLLER 32BIT 225BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21261 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Embedded Processor |

发布紧急采购,3分钟左右您将得到回复。