- 您现在的位置:买卖IC网 > PDF目录298899 > CA95C09-10CT TELECOM, DATA ENCRYPTION CIRCUIT, PQFP44 PDF资料下载

参数资料

| 型号: | CA95C09-10CT |

| 元件分类: | 加密电路 |

| 英文描述: | TELECOM, DATA ENCRYPTION CIRCUIT, PQFP44 |

| 封装: | TQFP-44 |

| 文件页数: | 29/42页 |

| 文件大小: | 180K |

| 代理商: | CA95C09-10CT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

Tundra Semiconductor Corporation

CA95C68/18/09

Tundra Semiconductor Corporation

3-59

Maximum Throughput

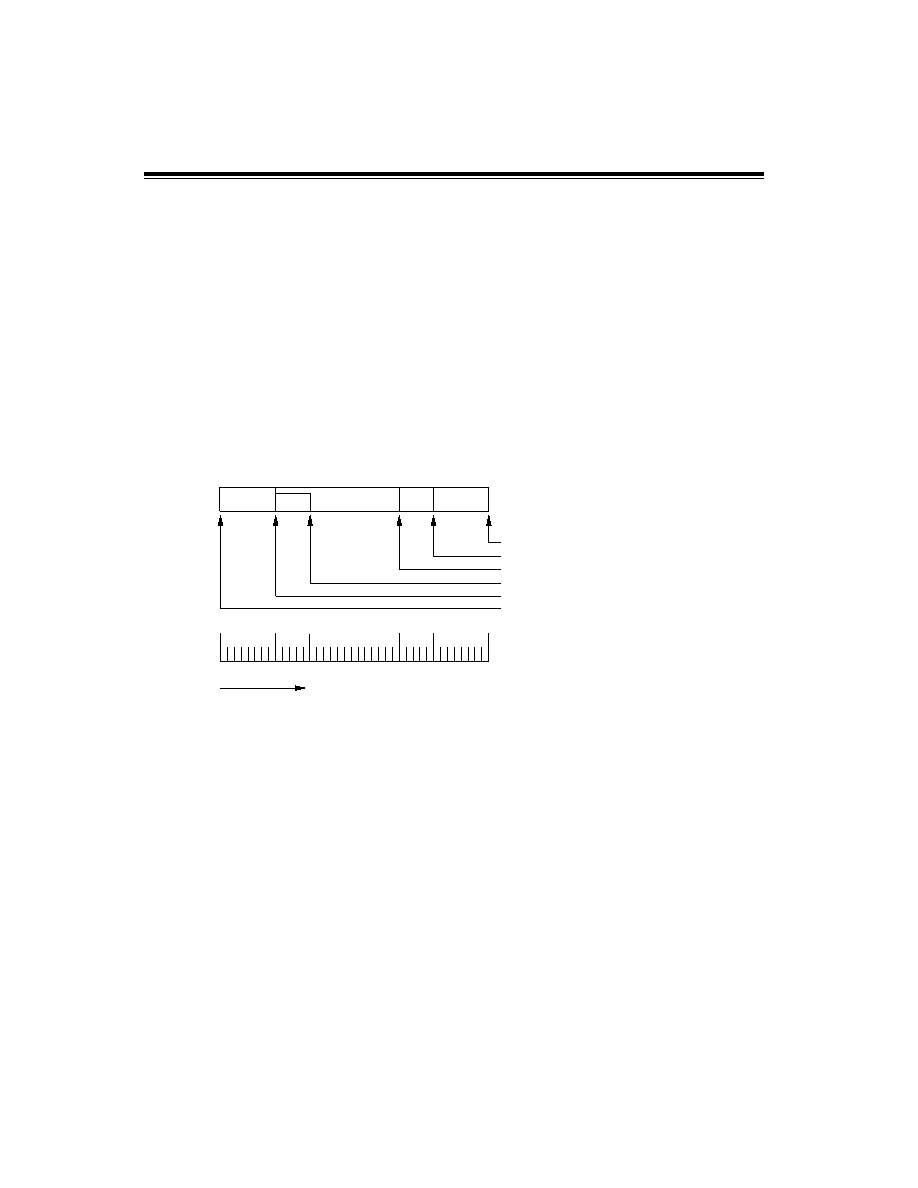

The pipelined architecture of the DES DCPs allows

simultaneous input, ciphering, and output operations.

Maximum throughput is obtained when the device is

congured for one of the dual port congurations. Figure 3-

22 shows the timing for ciphering one block of 64 bits in

either ECB or CBC modes of encryption. The inputting of

the 64 bits of data takes 8 clock cycles to complete with one

data strobe being issued per clock cycle. This data must then

be transferred from the Input Register to the algorithm

processing unit and the ags updated, which requires 5

additional clock cycles. The algorithm unit begins ciphering

concurrently with the transfer and once the ags have been

updated another 64 bit block may be entered. The ciphering

of the rst block is completed after 18 clock cycles have

elapsed from the last byte having been written to the Input

Register. Another 5 clock cycles are required to transfer the

ciphered data to the Output Register and update ags.

Transferring of data from the algorithm processing unit to

the Output Register can be performed concurrently with

loading new data into the DES algorithm unit. Removing the

data from the Output Register involves 8 clock cycles with

one data strobe per clock cycle. The whole procedure of

ciphering one block takes 39 cycles but because the different

operations can be overlapped, the DCP can process one

block every 18 clock cycles once fully loaded.

0

8

13

26

31

39

Clock

39 Finished reading 64-bit Block out of Output Port

31 Output Port FLAG becomes active

26 Algorithm Unit finishes processing block

13 Input Port FLAG becomes active for next Input Block

8 Algorithm Unit starts processing block

0 Start writing 64-bit Block into Input Port

Input 8

Bytes

In

Flags

Encryption/Decryption in

progress in the algorithm

unit

Out

Flags

Output

8 Bytes

Time in clock periods

Note: CA95C68 minimum clock period = 40 nanoseconds

Figure 3-22 : Detailed Timing of One Block

相关PDF资料 |

PDF描述 |

|---|---|

| CA95C09-16CT | TELECOM, DATA ENCRYPTION CIRCUIT, PQFP44 |

| CA95C09-20CT | TELECOM, DATA ENCRYPTION CIRCUIT, PQFP44 |

| CA95C09-25CT | TELECOM, DATA ENCRYPTION CIRCUIT, PQFP44 |

| CA95C09-33CT | TELECOM, DATA ENCRYPTION CIRCUIT, PQFP44 |

| CA95C09-5CT | TELECOM, DATA ENCRYPTION CIRCUIT, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CA96 | 制造商:Datak Corporation 功能描述: |

| CA9623-000 | 功能描述:CABLE RoHS:是 类别:线缆,导线 >> 同轴 系列:- 产品培训模块:General Cable 标准包装:1 系列:- 缆线类型:细电缆网 - 耐热阻燃型 缆线组:RG-58 线规:20 AWG(0.62mm²) 线束:19 股 / 32 AWG 套管类型:聚氯乙烯(PVC) 套管直径:0.186"(4.72mm) 屏蔽类型:箔,编织线 阻抗:50 欧姆 长度:100' (30.5m) 颜色:灰 使用:网络 特点:- 导线材料:铜,镀锡 电介质材料:多孔(泡沫)聚乙烯(多孔 FPE) 电介质直径:0.100"(2.54mm) 屏蔽材料:Flexfoil?; 铜,镀锡 屏蔽覆盖范围:100%,81% VoP,传输速度:80 工作温度:- 其它名称:C5779-100 |

| CA9652-000 | 制造商:TE Connectivity 功能描述:- Bulk |

| CA9681-000 | 制造商:TE Connectivity 功能描述:CA9681-000 |

| CA9809-000 | 制造商:TE Connectivity 功能描述:Heat Shrink Molded Boot 制造商:TE Connectivity 功能描述:222K142-25-CS-2101-0 - Bulk |

发布紧急采购,3分钟左右您将得到回复。