- 您现在的位置:买卖IC网 > PDF目录380066 > CS4103VHG (NATIONAL SEMICONDUCTOR CORP) IEEE P1394a Physical Layer Device PDF资料下载

参数资料

| 型号: | CS4103VHG |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | IEEE P1394a Physical Layer Device |

| 中文描述: | 3 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP80 |

| 封装: | LQFP-80 |

| 文件页数: | 1/24页 |

| 文件大小: | 423K |

| 代理商: | CS4103VHG |

2000 National Semiconductor Corporation

www.national.com

G

General Description

The National Semiconductor

Geode CS4103 is a three

port 400 Mbit/sec IEEE 1394 Physical Layer (PHY) device.

The CS4103 complies to revision 2.0 of the P1394a specifi-

cation. The device is a three port implementation of a reus-

able cell design scalable from one to sixteen ports.

The CS4103 supports all of the P1394a enhancements

including connection debounce, arbitrated reset, ack-accel-

erated arbitration, fly-by concatenation, multi-speed packet

concatenation, PHY pinging, priority arbitration, and Sus-

pend/Resume operation. It also implements the standard

PHY-Link interface defined in IEEE specification 1394-1995

and updated in the P1394a specification for direct connec-

tion with the Geode CS4210 IEEE 1394 Open Host Con-

troller Interface (OHCI) device. The interface can operate in

either direct or isolated mode and supports single capacitor

isolation with bus hold inputs.

The CS4103 provides a complete PHY solution including

all bias generation, differential line drivers and receivers,

single ended comparators for speed signaling, speed sig-

naling current sources, bias detect, and connect detect cir-

cuitry per port. It includes data and strobe encoding/

decoding functions as well as a re-time FIFO to synchro-

nize the receive data to the local clock domain. The

CS4103 can receive and respond to all the PHY packet

types defined in revision 2.0 of the P1394a specification. It

also supports Suspend and Resume port states and con-

nect detect functions.

The CS4103 generates the internal clocks and the Link

SCLK (System Clock) based on a 24.576 MHz external

crystal or a 24.576 MHz clock input. The CS4103 operates

from a single 3.3V supply and supports transfers at 98.304,

196.608, and 393.216 Mbit/sec, (usually referred to as 100,

200, and 400 Mbit/sec respectively).

Features

IEEE 1394 Physical Layer Device (PHY) compliant with

revision 2.0 of P1394a including all enhancements

Scalable design from one to sixteen ports

Supports data rates of 100, 200, and 400 Mbit/sec

Single 3.3V supply operation

Internal PLL generates SCLK and all internal clocks

from a single 24.576 MHz crystal or clock

Includes Cable Power Sense comparator for cable

power monitoring

Compatible with the Geode CS4210 OHCI Controller

and other IEEE 1394 OHCI devices

Supports the isolated PHY-Link interface compliant with

1394-1995 and P1394a specifications

Single capacitor bus hold isolation\

Power saving modes

80-pin TQFP (Thin Quad Flat Pack)

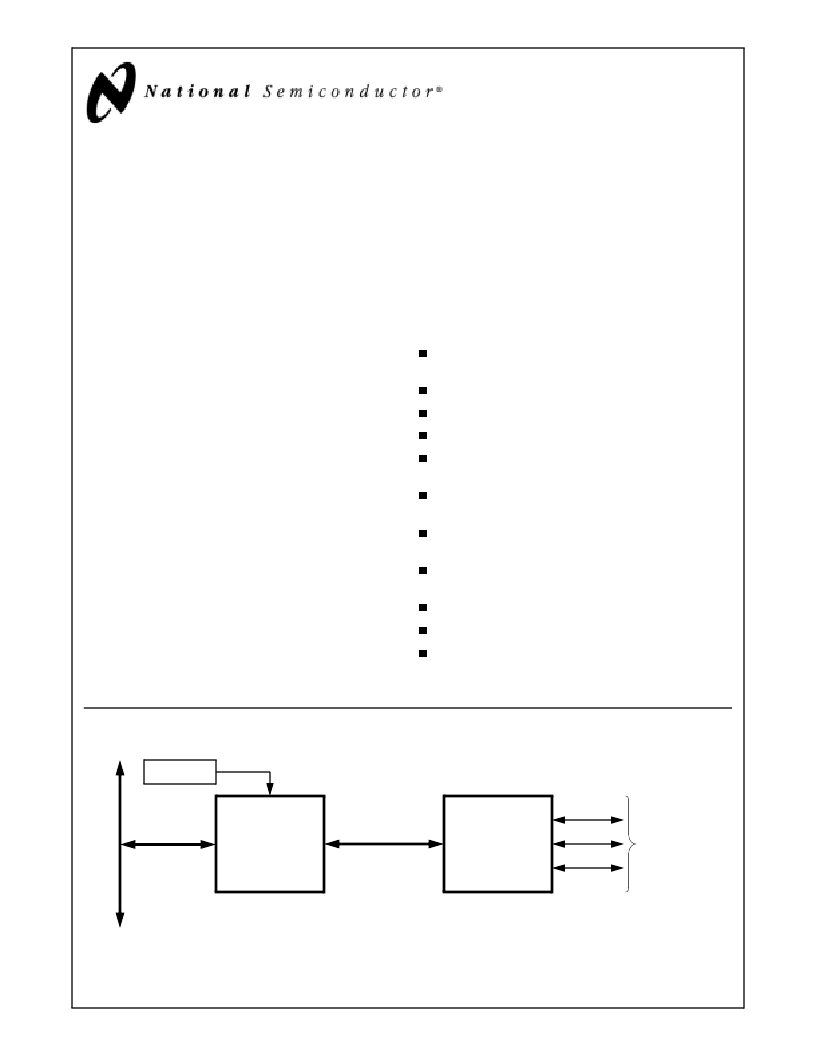

System Block Diagram

Geode CS4210

IEEE 1394

OHCI Controller

Geode CS4103

P1394a

Physical Layer

EEPROM

I

2

C Interface

PCI Interface

PHY-Link Interface

PCI Bus

IEEE 1394

Cable

Connectors

July 2000

Geode CS4103

IEEE P1394a Physical Layer Device

National Semiconductor is a registered trademark of National Semiconductor Corporation.

Geode is a trademark of National Semiconductor Corporation.

For a complete listing of National Semiconductor trademarks, please visit www.national.com/trademarks.

相关PDF资料 |

PDF描述 |

|---|---|

| CS4121EDWF20G | Low Voltage Precision Air-Core Tach/Speedo Driver |

| CS4122 | Triple Air-Core Gauge Driver with Serial Input Bus |

| CS4122XDWF24 | Triple Air-Core Gauge Driver with Serial Input Bus |

| CS4122XDWFR24 | Triple Air-Core Gauge Driver with Serial Input Bus |

| GS88136AD-150 | 512K x 18, 256K x 36 9Mb Synchronous Burst SRAMs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS41077DWR16 | 制造商:ON Semiconductor 功能描述: |

| CS41079DR8 | 制造商:ON Semiconductor 功能描述: |

| CS41080DR8G | 制造商:ON Semiconductor 功能描述:LINEAR IC |

| CS41082T5 | 制造商:ON Semiconductor 功能描述: |

| CS41083T5 | 制造商:ON Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。