- 您现在的位置:买卖IC网 > PDF目录380066 > CS4103VHG (NATIONAL SEMICONDUCTOR CORP) IEEE P1394a Physical Layer Device PDF资料下载

参数资料

| 型号: | CS4103VHG |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | IEEE P1394a Physical Layer Device |

| 中文描述: | 3 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP80 |

| 封装: | LQFP-80 |

| 文件页数: | 13/24页 |

| 文件大小: | 423K |

| 代理商: | CS4103VHG |

Revision 1.0

13

www.national.com

G

Register Descriptions

(Continued)

3.1

The register set of the CS4103 is accessed via the CS4210

OHCI

device’s

PHYControl

ECh[11:0]). The PHYControl register, shown in Table 3-2,

is used to read or write a CS4103 register.

REGISTER ACCESS

Register

(BAR0+Offset

To read a register, the address of the register is written to

the regAddr field along with a 1 in the rdReg bit. When the

read request has been sent to the CS4103 (through the

LREQ pin), the rdReg bit is cleared to 0. When the CS4103

returns the register, the rdDone bit transitions to 1 and the

IntEvent.phyRegRcvd interrupt (BAR0+Offset 80h[26]) is

set. The address of the register received is placed in the

rdAddr field and the contents in the rdData field. Software

must not issue a read of CS4103 base register at Address

00h (see Table 3-5 on page 14). The most recently avail-

able contents of this register is reflected in the NodeID reg-

ister (Table 3-3) of the CS4210.

To write to a CS4103 register, the address of the register is

written to the regAddr field, the value to write to the wrData

field, and a 1 to the wrReg bit. The wrReg bit is cleared

when the write request has been transferred to the

CS4103. Software must serialize all CS4103 register reads

and writes. Only after the current CS4103 register read or

write completes may software issue a different CS4103

register read or write.

For CS4210 register access information, refer to the

CS4210 data sheet.

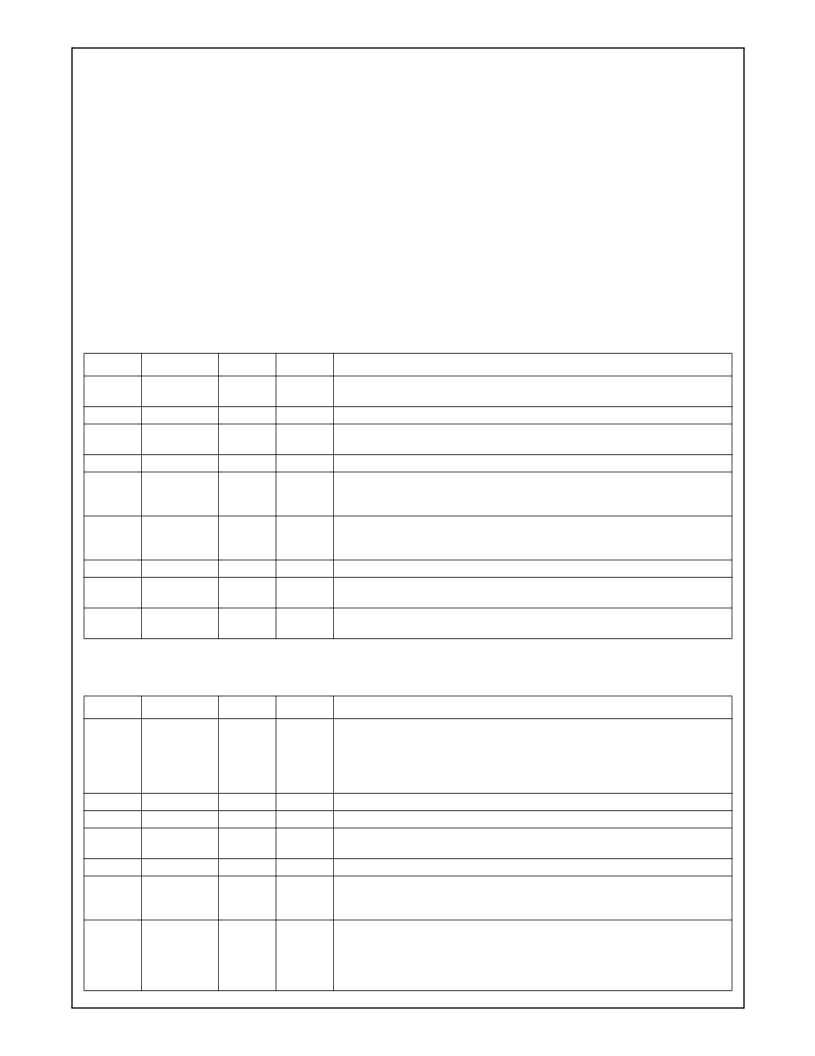

Table 3-2. CS4210 BAR0+Offset ECh: PHYControl Register

Bit

Name

Access

Reset

Description

31

rdDone

RU

Undef

Read Done:

rdDone is cleared to 0 by the CS4210 when either rdReg or wrReg is

set to 1. This bit is set to 1 when a register transfer is received from the CS4103.

Reserved

Read Address:

This is the address of the register most recently received from the

CS4103.

Read Data:

Contains the data read from the CS4103 register at rdAddr.

Read Register:

Set rdReg to initiate a read request to a CS4103 register. This bit

is cleared when the read request has been sent. The wrReg bit must not be set

while the rdReg bit is set.

Write Register:

Set wrReg to initiate a write request to a CS4103 register. This bit

is cleared when the write request has been sent. The rdReg bit must not be set

while the wrReg bit is set.

Reserved

Register Address:

regAddr is the address of the CS4103 register to be written or

read.

Write Data:

This is the contents to be written to a CS4103 register. Ignored for a

read.

30:28

27:24

RSVD

rdAddr

--

0

RU

Undef

23:16

15

rdData

rdReg

RU

RWU

Undef

0

14

wrReg

RWU

0

13:12

11:8

RSVD

regAddr

--

0

RW

Undef

7:0

wrData

RWU

Undef

Table 3-3. CS4210 BAR0+Offset E8h: Node ID and Status Register

Bit

Name

Access

Reset

Description

31

iDValid

RU

0

ID Valid:

This bit indicates whether or not the CS4210 has a valid node number. It

is cleared when the bus reset state is detected and set again when the CS4210

receives a new node number from the CS4103.

If iDValid is clear, software should not set ContextControl.run for either of the

ATDMA contexts (request and response).

Root:

This bit is set during the bus reset process if the CS4103 is root.

Reserved

Cable Power Status:

Set if the CS4103 is reporting that cable power status is OK

(VP 8V).

Reserved

Bus Number

: This number is used to identify the specific 1394 bus this node

belongs to when multiple 1394-compatible buses are connected via a bridge. This

field is set to 3FFh on a bus reset.

Node Number:

This number is the physical node number established by the

CS4103 during self-identification. It is automatically set to the value received from

the CS4103 after the self-identification phase. If the CS4103 sets the nodeNumber

to 63, software should not set ContextControl.run for either of the ATDMA contexts

(request and response).

30

root

RSVD

CPS

RU

--

RU

0

0

0

29:28

27

26:16

15:6

RSVD

busNumber

--

0

RWU

3FFh

5:0

nodeNumber

RU

Undef

相关PDF资料 |

PDF描述 |

|---|---|

| CS4121EDWF20G | Low Voltage Precision Air-Core Tach/Speedo Driver |

| CS4122 | Triple Air-Core Gauge Driver with Serial Input Bus |

| CS4122XDWF24 | Triple Air-Core Gauge Driver with Serial Input Bus |

| CS4122XDWFR24 | Triple Air-Core Gauge Driver with Serial Input Bus |

| GS88136AD-150 | 512K x 18, 256K x 36 9Mb Synchronous Burst SRAMs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS41077DWR16 | 制造商:ON Semiconductor 功能描述: |

| CS41079DR8 | 制造商:ON Semiconductor 功能描述: |

| CS41080DR8G | 制造商:ON Semiconductor 功能描述:LINEAR IC |

| CS41082T5 | 制造商:ON Semiconductor 功能描述: |

| CS41083T5 | 制造商:ON Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。