- 您现在的位置:买卖IC网 > PDF目录380066 > CS4103VHG (NATIONAL SEMICONDUCTOR CORP) IEEE P1394a Physical Layer Device PDF资料下载

参数资料

| 型号: | CS4103VHG |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | IEEE P1394a Physical Layer Device |

| 中文描述: | 3 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP80 |

| 封装: | LQFP-80 |

| 文件页数: | 9/24页 |

| 文件大小: | 423K |

| 代理商: | CS4103VHG |

Revision 1.0

9

www.national.com

G

Signal Definitions

(Continued)

2.2

SIGNAL DESCRIPTIONS

2.2.1

PHY-Link Interface Signals

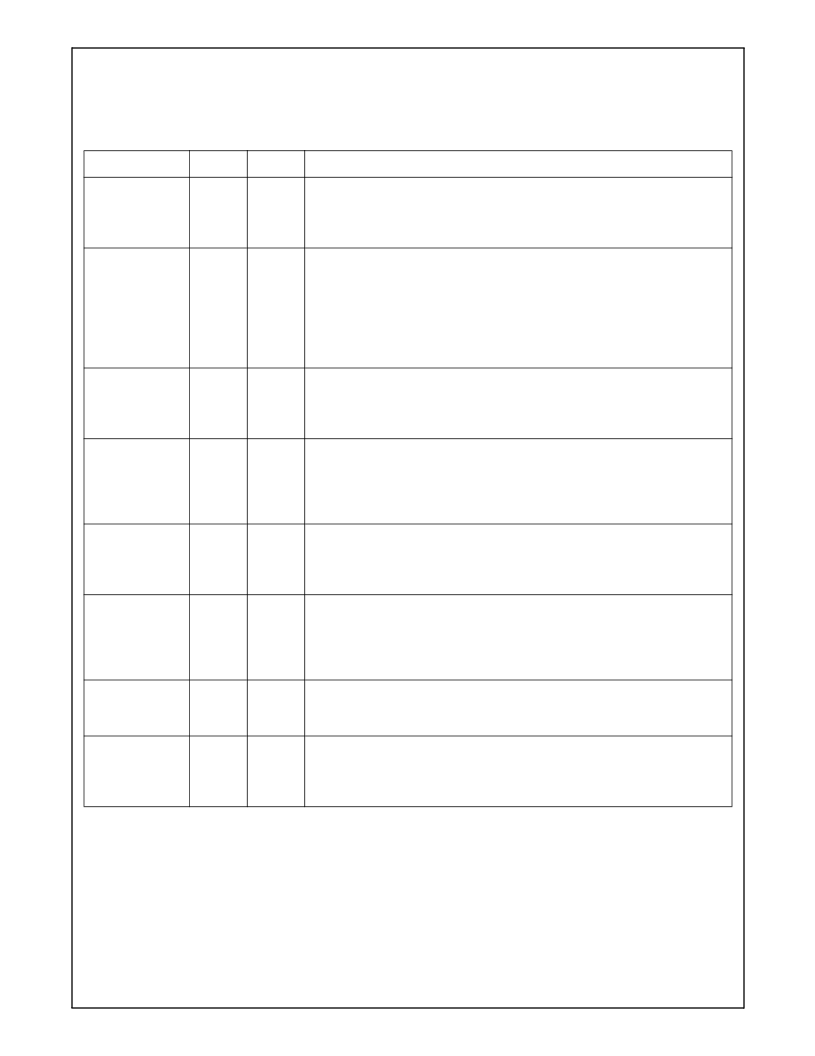

Signal Name

Pin

Type

Description

CTRL[0:1]

4, 5

I/O

Control Bits 0 and 1

The CS4103 uses CTRL[0:1] to signal PHY status transfers and packet recep-

tion transfers to the CS4210. The CS4103 grants control of the interface to the

CS4210 for packet transmission.

DATA[0:7]

7, 8,

10:15

I/O

Data Bits 0 through 7

DATA[0:1] are used for PHY status data transfers to the CS4210 and packet

transmit and receive. The width of the data bus depends on the speed of data

transfer rate. Packet rate for 100 Mbit/sec transfers use DATA[0:1], 200 Mbit/

sec transfers use DATA[0:3], 400 Mbit/sec transfers use DATA[0:7].

Note:

DATA0 is considered the MSB (most significant bit) based upon the

IEEE 1394-1995 specification.

LREQ

1

I

Link Request

The CS4103 receives serial bit stream requests from the CS4210 on this line.

The requests write PHY registers, request PHY register data, request packet

transmission, and control arbitration acceleration.

SCLK

2

O

System Clock

The 49.152 MHz clock output driven by the CS4103’s PLL block synchronized

to the 1394 bus clock. This clock is also used to synchronize the LREQ,

CTRL[0:1], and DATA[0:7] communication protocol between the CS4210 and

CS4103.

LPS

19

I

Link Power Status

The CS4210 signals the CS4103 to both reset and disable the PHY-Link inter-

face when this input is deaserted and to restore the interface when asserted.

This line is level driven in direct mode and pulsed in isolated mode.

LNKON

22

O

Link-On

The CS4103 uses this output to signal the CS4210 when the Link is inactive.

The Link is inactive when either LPS is deaserted or the PHY-Link_active bit

(Address 04h[0]) is zero. LNKON is a pulsed signal with a frequency from 4 to 8

MHz.

DIRECT

26

I

Direct/Isolation Barrier Indicator

Configures the PHY-Link interface to operate in direct/single capacitor bus hold

mode when high or isolated mode when low.

LOCKIND

17

I/O

PLL Lock Indicator

An output high on this pin indicates that the PLL is locked. This signal is infor-

mational and is not required for operation. For normal operation, this pin may

be disconnected.

相关PDF资料 |

PDF描述 |

|---|---|

| CS4121EDWF20G | Low Voltage Precision Air-Core Tach/Speedo Driver |

| CS4122 | Triple Air-Core Gauge Driver with Serial Input Bus |

| CS4122XDWF24 | Triple Air-Core Gauge Driver with Serial Input Bus |

| CS4122XDWFR24 | Triple Air-Core Gauge Driver with Serial Input Bus |

| GS88136AD-150 | 512K x 18, 256K x 36 9Mb Synchronous Burst SRAMs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS41077DWR16 | 制造商:ON Semiconductor 功能描述: |

| CS41079DR8 | 制造商:ON Semiconductor 功能描述: |

| CS41080DR8G | 制造商:ON Semiconductor 功能描述:LINEAR IC |

| CS41082T5 | 制造商:ON Semiconductor 功能描述: |

| CS41083T5 | 制造商:ON Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。