- 您现在的位置:买卖IC网 > PDF目录380066 > CS4103VHG (NATIONAL SEMICONDUCTOR CORP) IEEE P1394a Physical Layer Device PDF资料下载

参数资料

| 型号: | CS4103VHG |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | IEEE P1394a Physical Layer Device |

| 中文描述: | 3 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP80 |

| 封装: | LQFP-80 |

| 文件页数: | 10/24页 |

| 文件大小: | 423K |

| 代理商: | CS4103VHG |

www.national.com

10

Revision 1.0

G

Signal Definitions

(Continued)

2.2.2

Transceiver/1394 Cable Connection Signals

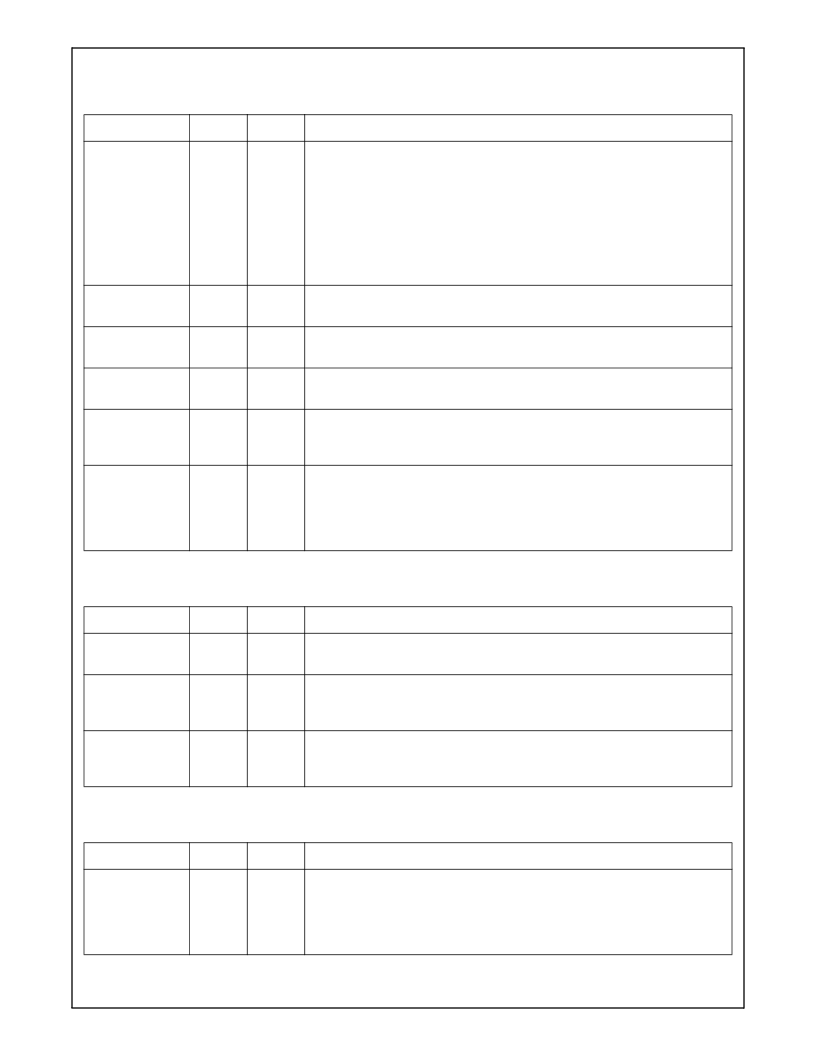

Signal Name

Pin

Type

Description

TPB[0:2]–

42, 49,

55

I/O

Negative Differential Signals for Port 0-2 Cable Pair B

Differential signal skew should be minimized by matching trace lengths within

the TPA and TPB differential pairs. In addition, TPA pair trace lengths should be

matched as closely as possible to TPB pair trace lengths within a port. Imped-

ance discontinuities may be minimized by routing TP lines primarily on the top

layer of the PCB. TP signal traces should have an impedance of 55 ohms to

analog ground and the analog ground plane should be continuous under the

TP traces. Minimize stub length by placing termination networks as close to the

CS4103 as possible.

TPB[0:2]+

43, 50,

56

I/O

Positive Differential Signals for Port 0-2 Cable Pair B

Refer to TPB[0:2]– signal description.

TPA[0:2]–

44, 51,

57

I/O

Negative Differential Signals for Port 0-2 Cable Pair A

Refer to TPB[0:2]– signal description.

TPA[0:2]+

45, 52,

58

I/O

Positive Differential Signals for Port 0-2 Cable Pair A

Refer to TPB[0:2]– signal description.

TPBIAS[0:2]

46, 53,

59

I/O

Twisted Pair Bias for Port 0-2

Bias generator output and connection detect input for the ports. Increase the

PCB trace widths on this line.

CPS

27

I

Cable Power Status Input

This comparator input detects valid cable power at voltages greater than 7.5V

and sets the PS (cable power active) bit (Address 00h[7]) in the CS4103 base

register. Voltages below 7.5V clear the PS bit. This pin is connected to a 402K

1% resistor to cable power and an 80.6K 1% resistor to ground.

2.2.3

Clock/Crystal Connection and Reset Signals

Signal Name

Pin

Type

Description

XI

76

I

Xtal In

Clock or crystal input connection 24.576 MHz (+/-100 ppm).

XO

77

O

Xtal Out

24.576 MHz crystal connection. If a clock is connected to XI, XO is discon-

nected.

RESET#

78

I

Active Low Reset Input

This pin is connected to a 56K resistor to VDD and a 0.1 μF capacitor to ground

yielding a power-on reset of approximately 3 ms.

2.2.4

Power to/from Bus Signals

Signal Name

Pin

Type

Description

PC[0:2]

23, 24,

25

I

Power Class Indicator 0 (MSB) through 2 (LSB)

The PC[0:2] pins are strapped to indicate power consumed from or supplied to

the bus (see P1394a specification, Table 8-3). At power-on the PC pins are

read and the Pwr_class field (Address 04h[5:7]) is set. This value is transmitted

in the pwr field of Self-ID packet zero.

相关PDF资料 |

PDF描述 |

|---|---|

| CS4121EDWF20G | Low Voltage Precision Air-Core Tach/Speedo Driver |

| CS4122 | Triple Air-Core Gauge Driver with Serial Input Bus |

| CS4122XDWF24 | Triple Air-Core Gauge Driver with Serial Input Bus |

| CS4122XDWFR24 | Triple Air-Core Gauge Driver with Serial Input Bus |

| GS88136AD-150 | 512K x 18, 256K x 36 9Mb Synchronous Burst SRAMs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS41077DWR16 | 制造商:ON Semiconductor 功能描述: |

| CS41079DR8 | 制造商:ON Semiconductor 功能描述: |

| CS41080DR8G | 制造商:ON Semiconductor 功能描述:LINEAR IC |

| CS41082T5 | 制造商:ON Semiconductor 功能描述: |

| CS41083T5 | 制造商:ON Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。