- 您现在的位置:买卖IC网 > PDF目录380066 > CS4103VHG (NATIONAL SEMICONDUCTOR CORP) IEEE P1394a Physical Layer Device PDF资料下载

参数资料

| 型号: | CS4103VHG |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | IEEE P1394a Physical Layer Device |

| 中文描述: | 3 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP80 |

| 封装: | LQFP-80 |

| 文件页数: | 14/24页 |

| 文件大小: | 423K |

| 代理商: | CS4103VHG |

www.national.com

14

Revision 1.0

G

Register Descriptions

(Continued)

3.2

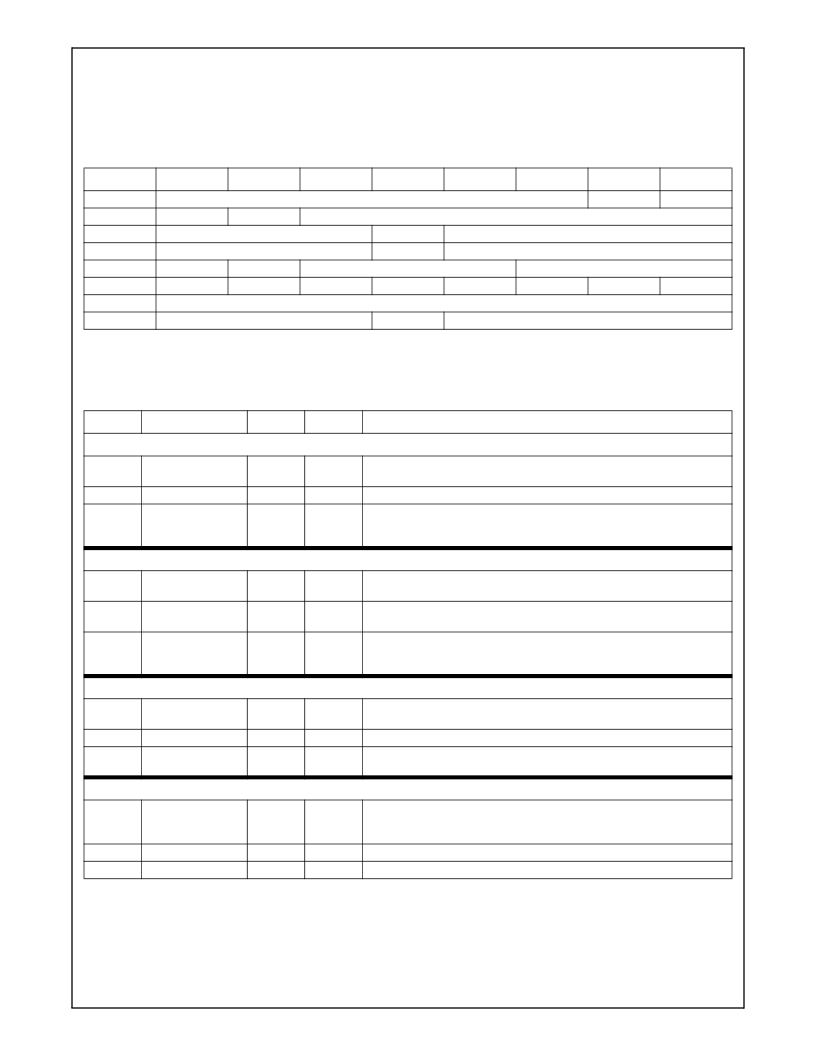

Table 3-4 is a register map of the CS4103’s Base registers. Table 3-5 provides the bit formats for these registers.

BASE REGISTER DESCRIPTIONS

Table 3-4. Base Register Bit Map

Address

0

1

2

3

4

5

6

7

00h

01h

02h

03h

04h

05h

06h

07h

Physical_ID

R

PS

RHB

IBR

Gap_count

Extended

Max_speed

Contender

ISBR

RSVD

RSVD

Jitter

Pwr_fail

Total_ports

Delay

Link_active

Resume_int

Pwr_class

Enab_accel

Loop

Timeout

Port_event

Enab_multi

RSVD

Page_select

RSVD

Port_select

Table 3-5. Base Registers

Bit

Name

Access

Reset

Description

Address 00h

0:5

Physical_ID

R

Undef

Physical ID:

The CS4103’s node address determined during self-identifica-

tion.

Root:

Set when the node becomes root.

Cable Power Active:

This bit is set when cable power is detected above

7.5V. If cable power drops below 7.5V the PS bit will be cleared and the

Pwr_fail bit set.

6

7

R

PS

R

R

Undef

Undef

Address 01h

0

RHB

RW

0

Root Hold-off Bit:

When set, the CS4103 will attempt to become root during

the next tree identify process which is subsequent to a bus reset.

Initiate Bus Reset:

When set, a non-arbitrated long bus reset of 167 μs will

be issued by the CS4103. This bit is self clearing.

Gap Count:

Arbitration gap times are tuned to minimize bus idle time with

this field. Gap times may be optimized for a specific bus configuration. Two

bus resets return gap_count to 3Fh.

1

IBR

RW

0

2:7

Gap_count

RW

3Fh

Address 02h

0:2

Extended

R

111

Extended:

A value of seven is assigned to this field indicating that the

extended PHY register map has been implemented.

Reserved

Total Ports:

This field shows the number of ports implemented by the

CS4103. The CS4103 utilizes three ports.

3

RSVD

Total_ports

--

R

--

4:7

1100

Address 03h

0:2

Max_speed

R

010

Maximum Speed:

Indicates CS4103 operational speeds. A value of 010

indicates the CS4103 supports 98.304, 196.608, and 393.216Mbit/sec oper-

ation.

Reserved

Delay:

Worst-case repeater delay equals 144 + (delay * 20) ns.

3

RSVD

Delay

--

R

--

4:7

0000

相关PDF资料 |

PDF描述 |

|---|---|

| CS4121EDWF20G | Low Voltage Precision Air-Core Tach/Speedo Driver |

| CS4122 | Triple Air-Core Gauge Driver with Serial Input Bus |

| CS4122XDWF24 | Triple Air-Core Gauge Driver with Serial Input Bus |

| CS4122XDWFR24 | Triple Air-Core Gauge Driver with Serial Input Bus |

| GS88136AD-150 | 512K x 18, 256K x 36 9Mb Synchronous Burst SRAMs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS41077DWR16 | 制造商:ON Semiconductor 功能描述: |

| CS41079DR8 | 制造商:ON Semiconductor 功能描述: |

| CS41080DR8G | 制造商:ON Semiconductor 功能描述:LINEAR IC |

| CS41082T5 | 制造商:ON Semiconductor 功能描述: |

| CS41083T5 | 制造商:ON Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。