参数资料

| 型号: | CS80C286-16 |

| 厂商: | Intersil |

| 文件页数: | 32/60页 |

| 文件大小: | 0K |

| 描述: | IC CPU 16BIT 5V 16MHZ 68-PLCC |

| 标准包装: | 126 |

| 处理器类型: | 80C286 16-位 |

| 速度: | 16MHz |

| 电压: | 5V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 68-LCC(J 形引线) |

| 供应商设备封装: | 68-PLCC(24.23x24.23) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

38

NOTES:

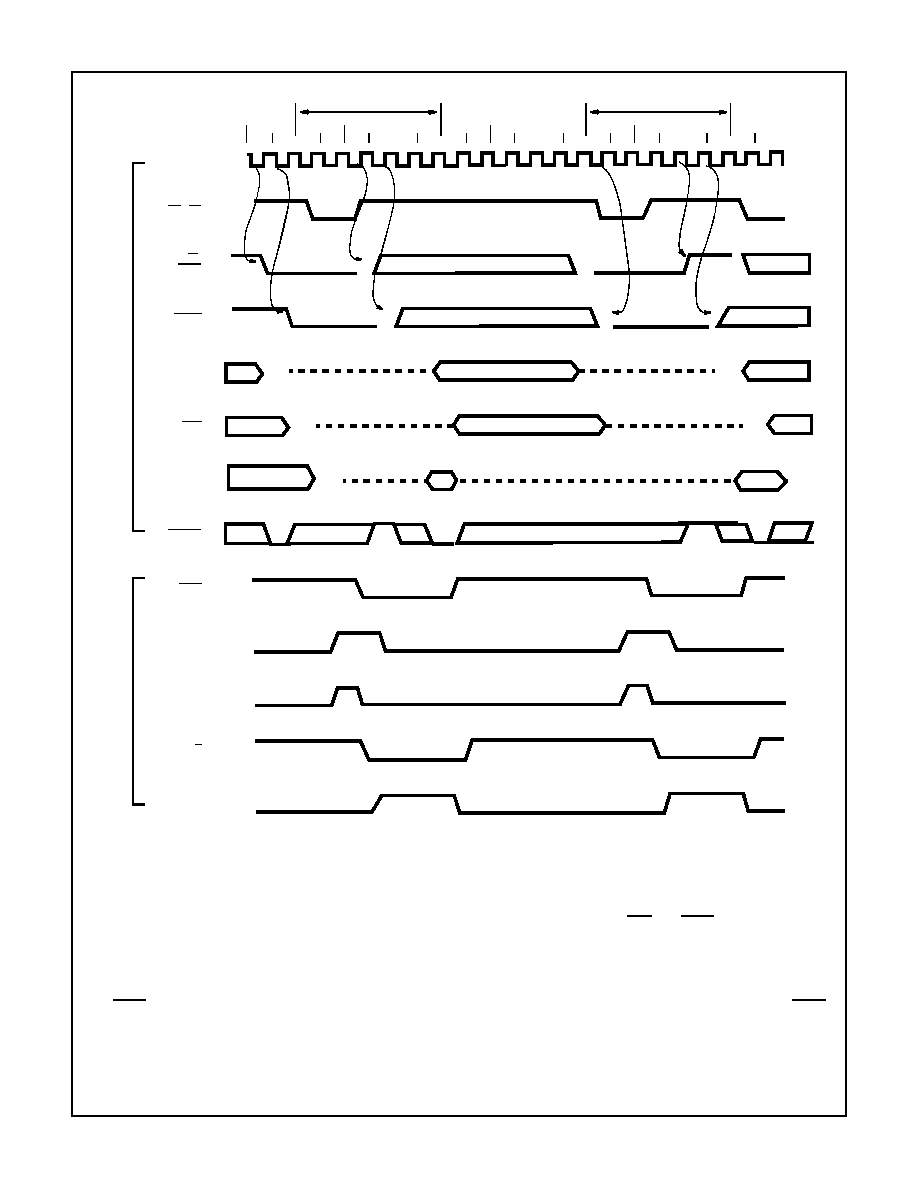

18. Data is ignored.

19. First INTA cycle should have at least one wait state inserted to meet 82C59A minimum INTA pulse width.

20. Second INTA cycle must have at least one wait state inserted since the CPA will not drive A23-A0, BHE, and LOCK until after the first TC

state. The CPU imposed one/clock delay prevents has contention between cascade address buffer being disabled by MCE

↓ and address

outputs.

21. Without the wait state, the 80C286 address will not be valid for a memory cycle started immediately after the second INTA cycle. The

82C59A also requires one wait state for minimum INTA pulse width.

22. LOCK is active for the first INTA cycle to prevent the 82289 from releasing the bus between INTA cycles in a multi-master system. LOCK

is also active for the second INTA cycle.

23. A23-A0 exits three-state OFF during φ2 of the second TC in the INTA cycle.

FIGURE 29. INTERRUPT ACKNOWLEDGE SEQUENCE

TC

φ2

φ1

INTA CYCLE 1

TS

φ2

φ1

TC

φ2

φ1

TC

φ2

φ1

TI

φ2

φ1

TI

φ2

φ1

TI

φ2

φ1

TS

φ2

φ1

TC

φ2

φ1

TC

φ2

φ1

TS

φ2

φ1

INTA CYCLE 2

BUS CYCLE

CLK

S1

S0

M/IO,

LOCK

A23 - A0

BHE

D15 - D0

READY

INTA

MCE

ALE

DT/R

DEN

(SEE NOTE 21)

(SEE NOTE 22)

DON’T CARE

PREVIOUS

WRITE CYCLE

(SEE NOTE 18)

VECTOR

(SEE NOTE 20)

NOT READY READY

(SEE NOTE 19)

NOT READY

READY

COD/INTA

TYPE

80C286

82C288

80C286

相关PDF资料 |

PDF描述 |

|---|---|

| ACB90DHAR | CONN EDGECARD 180PS R/A .050 DIP |

| MPC857TZQ66B | IC MPU PWRQUICC 66MHZ 357-PBGA |

| ABB95DHAS | CONN EDGECARD 190PS R/A .050 SLD |

| MPC857TVR66B | IC MPU POWERQUICC 66MHZ 357-PBGA |

| MPC8271ZQTIEA | IC MPU POWERQUICC II 516-PBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS80C286-1696 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-2 | 制造商:Harris Corporation 功能描述: |

| CS80C286-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-2096 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-20S2463 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。