- 您现在的位置:买卖IC网 > PDF目录171067 > DDP3315CQA (MICRONAS SEMICONDUCTOR HOLDING AG) SPECIALTY CONSUMER CIRCUIT, PQFP80 PDF资料下载

参数资料

| 型号: | DDP3315CQA |

| 厂商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封装: | PLASTIC, QFP-80 |

| 文件页数: | 39/62页 |

| 文件大小: | 1746K |

| 代理商: | DDP3315CQA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

ADVANCE INFORMATION

44

Micronas

4.3. Pin Descriptions

Pin 3, Enable 656 mode, 656EN (Fig. 4–3)

Low level selects parallel mode with LLC2 = 27/

32 MHz,

a

high

level

selects

656

mode

with

LLC2=54 MHz.

Pin 4, Main Clock Input, LLC2 (Fig. 4–3)

This is the input for the line-locked clock signal. The

frequency can be 27, 32, 40.5, 54 MHz.

Pin 5, Sync Signal Input, HS (Fig. 4–3)

This pin gets the horizontal sync information. Either

single or double horizontal frequency or VGA horizon-

tal sync signal.

Pin 6, Sync Signal Input, VS (Fig. 4–3)

This pin gets the vertical sync information. Either sin-

gle or double vertical frequency or VGA vertical sync

signal.

Pin 7, H-Drive frequency of range select, FREQSEL

This pin selects the frequency range for the horizontal

drive signal (see Section 2.3.2. on page 16).

Pin 8, Clock Select 1, CM1 (Fig. 4–3)

In case of a low level on 656EN, a low level on this pin

selects 27/32 MHz, a high level selects 40.5 MHz (see

Pin 9, Clock Select 0, CM0 (Fig. 4–3)

In case of a low level on 656EN, a low level on this pin

selects 27 MHz, a high level selects 32 MHz (see Sec-

Pin 10, Sync Signal Input, VS2 (Fig. 4–3)

Additional pin for the vertical sync information. Via I2C-

Register the used vertical sync can be switched

between the inputs VS2 and VS (Pin 6)

These Pins are connected to an 5 MHz crystal oscilla-

tor. The security unit for the HOUT signal uses this

clock signal as reference.

Pin 14, Ground, Output Pin Driver, GNDP1)

Output Pin Driver Reference

Pin 15, Supply Voltage, Output Pin Driver, VSUPP1)

This pin is used as supply for the following digital out-

put pins: FIFORRD, FIFORD, FIFOWR, FIFORWR,

PWM1, PWM2, PWMV, HOUT, DFVBL, HSYNC,

VSYNC.

Pin 16, Reset for FIFO read counter, FIFORRD

This signal is active high and resets the read counter

in the display frequency doubling FIFO.

This signal is active high and enables the read counter

in the display frequency doubling FIFO.

This signal is active high and enables the write counter

in the display frequency doubling FIFO.

Pin 19, Reset for FIFO write counter, FIFORWR

This signal is active high and resets the write counter

in the display frequency doubling FIFO.

Pin 20, Adjustable DC Output 1, PWM1 (Fig. 4–4)

This output delivers a DC voltage with a resolution of

8 bit, adjustable over the I2C bus. The output is driven

by a push-pull stage. The PWM frequency is appr.

79.4 kHz. For a ripple-free voltage a first order low-

pass filter with a corner frequency < 120 Hz should be

applied.

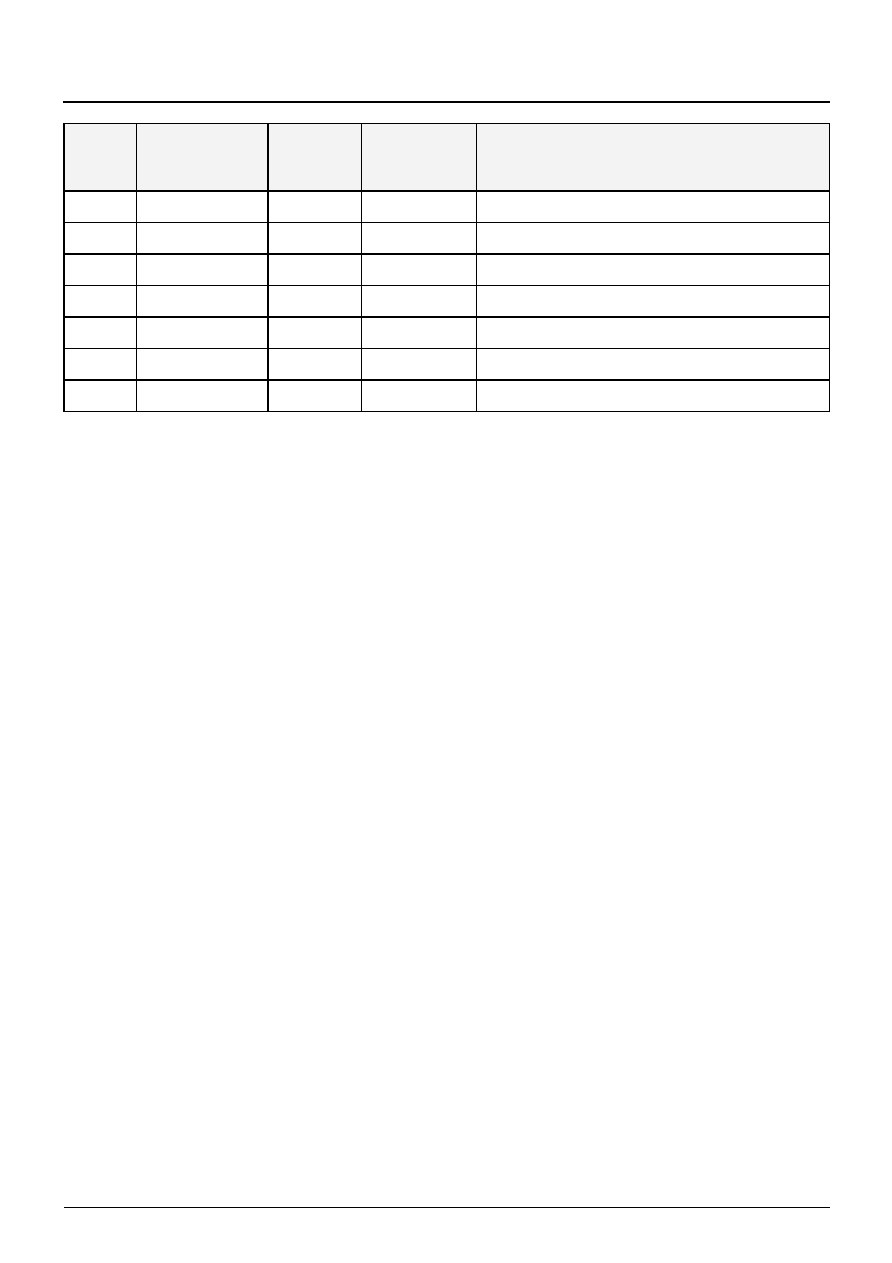

74

GNDD

SUPPLYD

X

Ground, Digital Circuitry

75

Y0

IN

GNDD

Picture Bus Luma (LSB)

76

Y1

IN

GNDD

Picture Bus Luma

77

Y2

IN

GNDD

Picture Bus Luma

78

Y3

IN

GNDD

Picture Bus Luma

79

Y4

IN

GNDD

Picture Bus Luma

80

Y5

IN

GNDD

Picture Bus Luma

Pin No.

Pin Name

Type

Connection

Short Description

PQFP

80-pin

(if not used)

相关PDF资料 |

PDF描述 |

|---|---|

| DDQ24W7P043A00LF | 24 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR, SOLDER |

| DDQ24W7PA00LF | 24 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR, SOLDER |

| DDQ36W4P043A00LF | 36 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR, SOLDER |

| DDQ36W4PA00LF | 36 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR, SOLDER |

| DDQ47W1P043A00LF | 47 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR, SOLDER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DDP-37CT | 制造商:Pan Pacific 功能描述: |

| DDP400-P1 | 制造商:CCM Assembly & Manufacturing 功能描述:AC Input Cable for ROAL DDP400 series, Bulk |

| DDP400-P4 | 制造商:CCM Assembly & Manufacturing 功能描述:DC Output Cable for ROAL DDP400 series, Bulk |

| DDP400-P6 | 制造商:CCM Assembly & Manufacturing 功能描述:Signal Cable for ROAL DDP400 series, Bulk |

| DDP400-US12-FF | 制造商:ROAL Electronics 功能描述:AC/DC 400W 12V Single Output Enclosed Front Fan, Bulk |

发布紧急采购,3分钟左右您将得到回复。