- 您现在的位置:买卖IC网 > Datasheet目录409 > DR-TRC105-450-EV (RFM)BOARD EVALUATION 450MHZ RFM RFIC Datasheet资料下载

参数资料

| 型号: | DR-TRC105-450-EV |

| 厂商: | RFM |

| 文件页数: | 16/67页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION 450MHZ RFM RFIC |

| 标准包装: | 1 |

| 类型: | 收发器 |

| 频率: | 447MHz ~ 451MHz |

| 适用于相关产品: | TRC105 |

| 已供物品: | 2 个板,天线,电池 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页

�� �

�

�

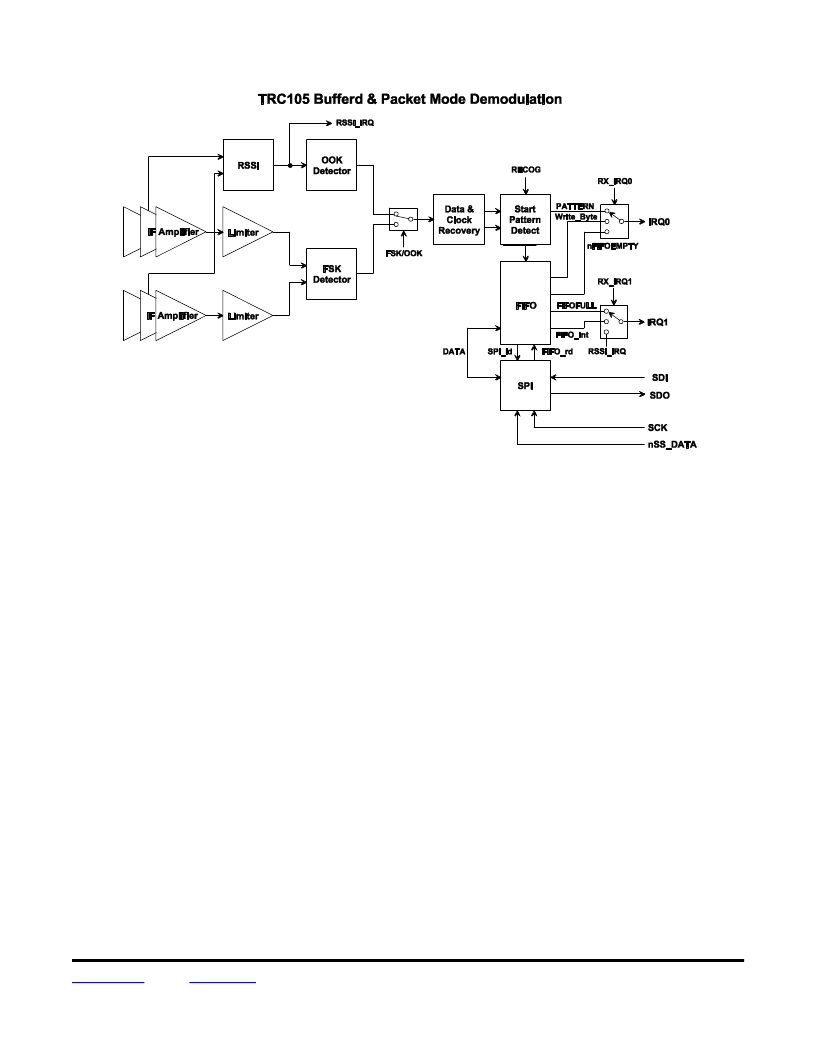

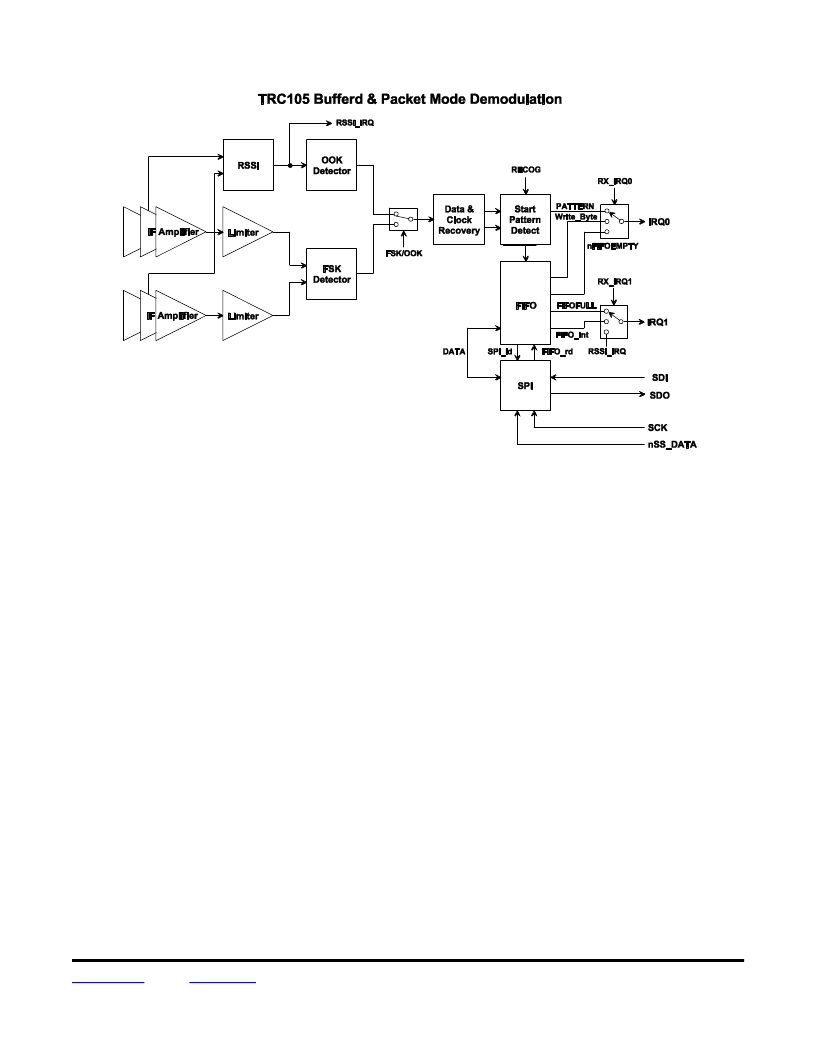

�Figure� 11�

�When� the� TRC105� is� in� receive� mode� and� MCFG01_Mode� [7..6� ]� bits� are� set� to� 01,� all� of� the� blocks� described�

�above� are� enabled.� In� a� normal� communication� frame� the� data� stream� is� comprised� of� a� 24-bit� preamble,� a� start�

�pattern� and� data.� Upon� receipt� of� a� matching� start� pattern� the� receiver� recognizes� the� start� of� data,� strips� off� the�

�preamble� and� start� pattern,� and� stores� the� data� in� the� FIFO� for� retrieval� by� the� host� microcontroller.� This� automat-�

�ed� data� extraction� reduces� the� loading� on� the� host� microcontroller.�

�The� IRQCFG0E_Start_Fill[7]� bit� determines� how� the� FIFO� is� filled.� If� IRQCFG0E_Start_Fill[7]� is� set� to� 0,� data�

�only� fills� the� FIFO� when� a� start� pattern� is� detected.� Received� data� bits� are� shifted� into� the� pattern� recognition�

�block� which� continuously� compares� the� received� data� with� the� contents� of� the� SYNCFG� registers.� If� a� match� oc-�

�curs,� the� start� pattern� detect� block� output� is� set� for� one� bit� period� and� the� IRQCFG0E_Start_Det[6]� bit� is� also� set.�

�This� internal� signal� can� be� mapped� to� the� IRQ0� output� using� interrupt� signal� mapping.� Once� a� pattern� match� has�

�occurred,� the� start� pattern� detect� block� will� remain� inactive� until� the� IRQCFG0E_Start_Det[6]� bit� is� reset.�

�If� IRQCFG0E_Start_Fill[7]� is� set� to� 1,� FIFO� filling� is� initiated� by� asserting� IRQCFG0E_Start_Det[6]� .� Once� 64�

�bytes� have� been� written� to� the� FIFO� the� IRQCFG0D_FIFOFULL[1]� signal� is� set.� Data� should� then� be� read� out.� If�

�no� action� is� taken,� the� FIFO� will� overflow� and� subsequent� data� will� be� lost.� If� this� occurs� the� IRQCFG0E_FIFO_�

�OVR[4]� bit� is� set� to� 1.� The� IRQCFG0D_FIFOFULL[1]� signal� can� be� mapped� to� pin� IRQ1� as� an� interrupt� for� a� mi-�

�crocontroller� if� IRQCFG0D_RX_IRQ1[5..4]� is� set� to� 01.� To� recover� from� an� overflow,� a� 1� must� be� written� to�

�IRQCFG0D_� FIFO_OVR[4]� .� This� clears� the� contents� of� the� FIFO,� resets� all� FIFO� status� flags� and� re-initiates� pat-�

�tern� detection.� Pattern� detection� can� also� be� re-initiated� during� a� FIFO� filling� sequence� by� writing� a� 1� to�

�IRQCFG0E_Start_Det[6]� .�

�The� details� of� the� FIFO� filling� process� are� shown� in� Figure� 12.� As� the� first� byte� is� written� into� the� FIFO,� signal�

�IRQCFG0D_nFIFOEMPY[0]� is� set� indicating� at� least� one� byte� is� present.� The� host� microcontroller� can� then� read�

�the� contents� of� the� FIFO� through� the� SPI� interface.� When� all� data� is� read� from� the� FIFO,� IRQCFG0D_�

�www.RFM.com� E-mail:� info@rfm.com�

�?� 2009-2013� by� RF� Monolithics,� Inc.�

�Technical� support� +1.800.704.6079�

�Page� 16� of� 67�

�TRC105� -� 05/29/13�

�相关PDF资料 |

PDF描述 |

|---|---|

| DR-TXC100-433 | BOARD EVALUATION 433MHZ TXC100 |

| DR-WLS1273L-EV | KIT EVAL FOR WLS1273L |

| DR7000-DK | 3G DEVELOPMENT KIT 433.92MHZ |

| DR7001-DK | 3G DEVELOPMENT KIT 315 MHZ |

| DR7003-DK | 3G DEVELOPMENT KIT 303.825 MHZ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DRTU06D06 | 功能描述:时间延迟和计时继电器 180-240VAC/DC 1-60VDC 6A RoHS:否 制造商:Crydom 显示器类型:Hand Dial 电源电压:280 VAC 定时范围: 触点形式: 触点额定值:6 A 端接类型:DIN Rail |

| DRTU24A06 | 功能描述:时间延迟和计时继电器 180-240VAC/DC 24-280VAC 6A RoHS:否 制造商:Crydom 显示器类型:Hand Dial 电源电压:280 VAC 定时范围: 触点形式: 触点额定值:6 A 端接类型:DIN Rail |

| DRTU24A06R | 功能描述:时间延迟和计时继电器 90-140VAC/DC 24-280VAC 6A RoHS:否 制造商:Crydom 显示器类型:Hand Dial 电源电压:280 VAC 定时范围: 触点形式: 触点额定值:6 A 端接类型:DIN Rail |

| DRTU24B06 | 功能描述:时间延迟和计时继电器 90-140VAC/DC 24-280VAC 6A RoHS:否 制造商:Crydom 显示器类型:Hand Dial 电源电压:280 VAC 定时范围: 触点形式: 触点额定值:6 A 端接类型:DIN Rail |

| DRTU24B06R | 功能描述:时间延迟和计时继电器 2-24VAC/DC 24-280VAC 6A RoHS:否 制造商:Crydom 显示器类型:Hand Dial 电源电压:280 VAC 定时范围: 触点形式: 触点额定值:6 A 端接类型:DIN Rail |

发布紧急采购,3分钟左右您将得到回复。