- 您现在的位置:买卖IC网 > Datasheet目录409 > DR-TRC105-450-EV (RFM)BOARD EVALUATION 450MHZ RFM RFIC Datasheet资料下载

参数资料

| 型号: | DR-TRC105-450-EV |

| 厂商: | RFM |

| 文件页数: | 27/67页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION 450MHZ RFM RFIC |

| 标准包装: | 1 |

| 类型: | 收发器 |

| 频率: | 447MHz ~ 451MHz |

| 适用于相关产品: | TRC105 |

| 已供物品: | 2 个板,天线,电池 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页

�� �

�

�

�Figure� 20� shows� the� timing� diagram� for� a� single� byte� write� sequence� to� the� TRC105� through� the� SPI� configuration�

�interface.� Note� that� nSS_CONFIG� must� remain� low� during� the� transmission� of� the� two� bytes� (address� and� data).� If�

�it� goes� high� after� the� first� byte,� then� the� next� byte� will� be� considered� as� an� address� byte.� When� writing� to� more�

�than� one� register� successively,� nSS_CONFIG� does� not� need� to� have� a� high-to-low� transition� between� two� write�

�sequences.� The� bytes� are� alternatively� considered� as� an� address� byte� followed� by� a� data� byte.�

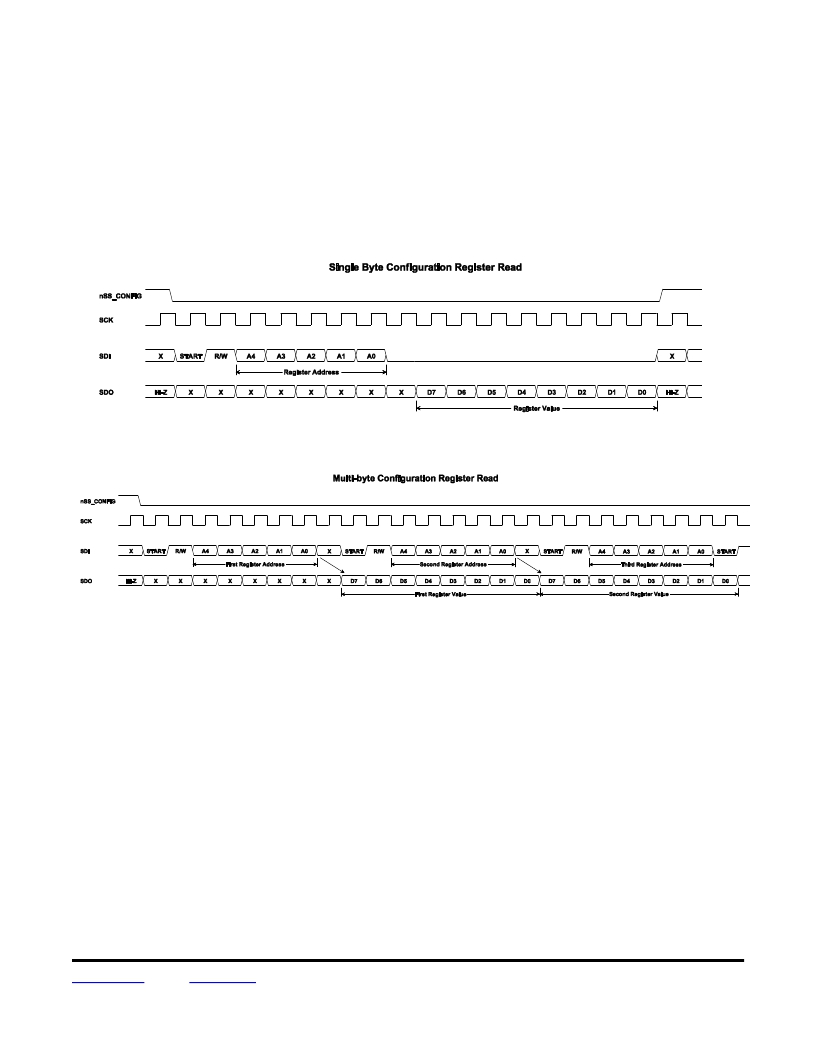

�The� read� sequence� through� the� SPI� configuration� interface� is� similar� to� the� write� sequence.� The� host� microcon-�

�troller� sends� the� address� during� the� first� SPI� communication� and� then� reads� the� data� during� a� second� SPI� com-�

�munication.� Note� that� 0� bits� can� be� input� to� the� SDI� during� the� second� SPI� communication� for� a� single� byte� read.�

�Figure� 21� shows� the� timing� diagram� for� a� single� byte� read� sequence� from� the� TRC105� through� the� SPI.�

�Figure� 21�

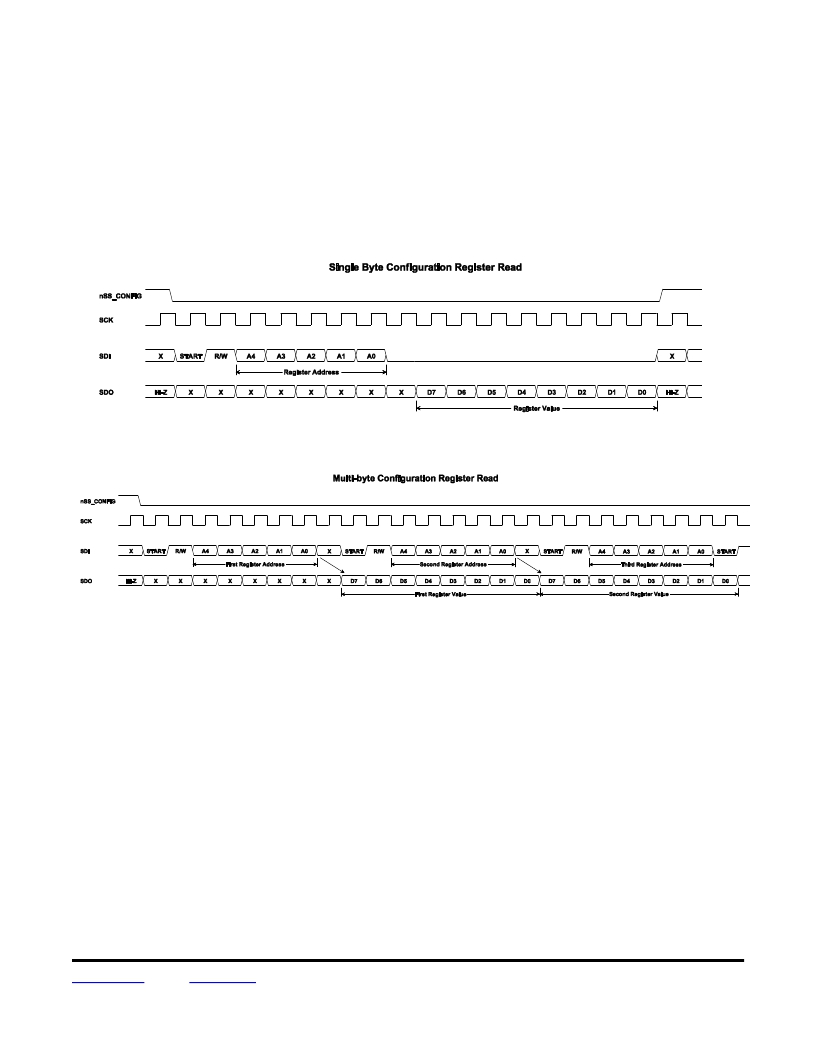

�Figure� 22�

�Multiple� configuration� register� reads� are� also� possible� by� sending� a� series� of� register� addresses� into� the� SPI� port,�

�as� shown� in� Figure� 22.�

�3.11� SPI� Data� FIFO� Interface�

�When� the� transceiver� is� used� in� Buffered� or� Packet� data� mode,� data� is� written� to� and� read� from� the� FIFO� through�

�the� SPI� interface.� Two� interrupts,� IRQ0� and� IRQ1,� are� used� to� manage� the� transfer� procedure.�

�When� the� transceiver� is� operating� in� Buffered� or� Packet� data� mode,� the� FIFO� interface� is� selected� when�

�nSS_DATA� is� set� to� 0� and� nSS_CONFIG� is� set� to� 1.� SPI� operations� with� the� FIFO� are� similar� to� operations� with�

�the� configuration� registers� with� two� important� exceptions.� First,� no� addresses� are� used� with� the� FIFO,� only� data�

�bytes� are� exchanged.� Second,� nSS_DATA� must� be� toggled� high� and� back� low� between� data� bytes� when� writing�

�to� the� FIFO� or� reading� from� the� FIFO.� Toggling� nSS_DATA� indexes� the� access� pointer� to� each� byte� in� the� FIFO� in�

�lieu� of� using� explicit� addressing.� Figure� 23� shows� the� timing� diagram� for� a� multiple-byte� write� sequence� to� the�

�TRC105� during� transmit,� and� Figure� 24� shows� the� timing� for� a� multi-byte� read� sequence.�

�www.RFM.com� E-mail:� info@rfm.com�

�?� 2009-2013� by� RF� Monolithics,� Inc.�

�Technical� support� +1.800.704.6079�

�Page� 27� of� 67�

�TRC105� -� 05/29/13�

�相关PDF资料 |

PDF描述 |

|---|---|

| DR-TXC100-433 | BOARD EVALUATION 433MHZ TXC100 |

| DR-WLS1273L-EV | KIT EVAL FOR WLS1273L |

| DR7000-DK | 3G DEVELOPMENT KIT 433.92MHZ |

| DR7001-DK | 3G DEVELOPMENT KIT 315 MHZ |

| DR7003-DK | 3G DEVELOPMENT KIT 303.825 MHZ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DRTU06D06 | 功能描述:时间延迟和计时继电器 180-240VAC/DC 1-60VDC 6A RoHS:否 制造商:Crydom 显示器类型:Hand Dial 电源电压:280 VAC 定时范围: 触点形式: 触点额定值:6 A 端接类型:DIN Rail |

| DRTU24A06 | 功能描述:时间延迟和计时继电器 180-240VAC/DC 24-280VAC 6A RoHS:否 制造商:Crydom 显示器类型:Hand Dial 电源电压:280 VAC 定时范围: 触点形式: 触点额定值:6 A 端接类型:DIN Rail |

| DRTU24A06R | 功能描述:时间延迟和计时继电器 90-140VAC/DC 24-280VAC 6A RoHS:否 制造商:Crydom 显示器类型:Hand Dial 电源电压:280 VAC 定时范围: 触点形式: 触点额定值:6 A 端接类型:DIN Rail |

| DRTU24B06 | 功能描述:时间延迟和计时继电器 90-140VAC/DC 24-280VAC 6A RoHS:否 制造商:Crydom 显示器类型:Hand Dial 电源电压:280 VAC 定时范围: 触点形式: 触点额定值:6 A 端接类型:DIN Rail |

| DRTU24B06R | 功能描述:时间延迟和计时继电器 2-24VAC/DC 24-280VAC 6A RoHS:否 制造商:Crydom 显示器类型:Hand Dial 电源电压:280 VAC 定时范围: 触点形式: 触点额定值:6 A 端接类型:DIN Rail |

发布紧急采购,3分钟左右您将得到回复。