- 您现在的位置:买卖IC网 > PDF目录11784 > DS80C400-FNY+ (Maxim Integrated Products)IC MCU 75MHZ 16MB HP 100-LQFP PDF资料下载

参数资料

| 型号: | DS80C400-FNY+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 55/97页 |

| 文件大小: | 0K |

| 描述: | IC MCU 75MHZ 16MB HP 100-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 90 |

| 系列: | 80C |

| 核心处理器: | 8051 |

| 芯体尺寸: | 8-位 |

| 速度: | 75MHz |

| 连通性: | 1 线,CAN,EBI/EMI,以太网,SIO,UART/USART |

| 外围设备: | 电源故障复位,WDT |

| 输入/输出数: | 64 |

| 程序存储器容量: | 64KB(64K x 8) |

| 程序存储器类型: | ROM |

| RAM 容量: | 1K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 1.62 V ~ 3.6 V |

| 振荡器型: | 外部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 100-LQFP |

| 包装: | 托盘 |

| 配用: | DS80C400-KIT#-ND - EVAL KIT FOR DS80C400 |

| 其它名称: | DS80C400+FNY DS80C400+FNY+ DS80C400+FNY+-ND DS80C400+FNY-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页当前第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页

DS80C400 Network Microcontroller

59 of 97

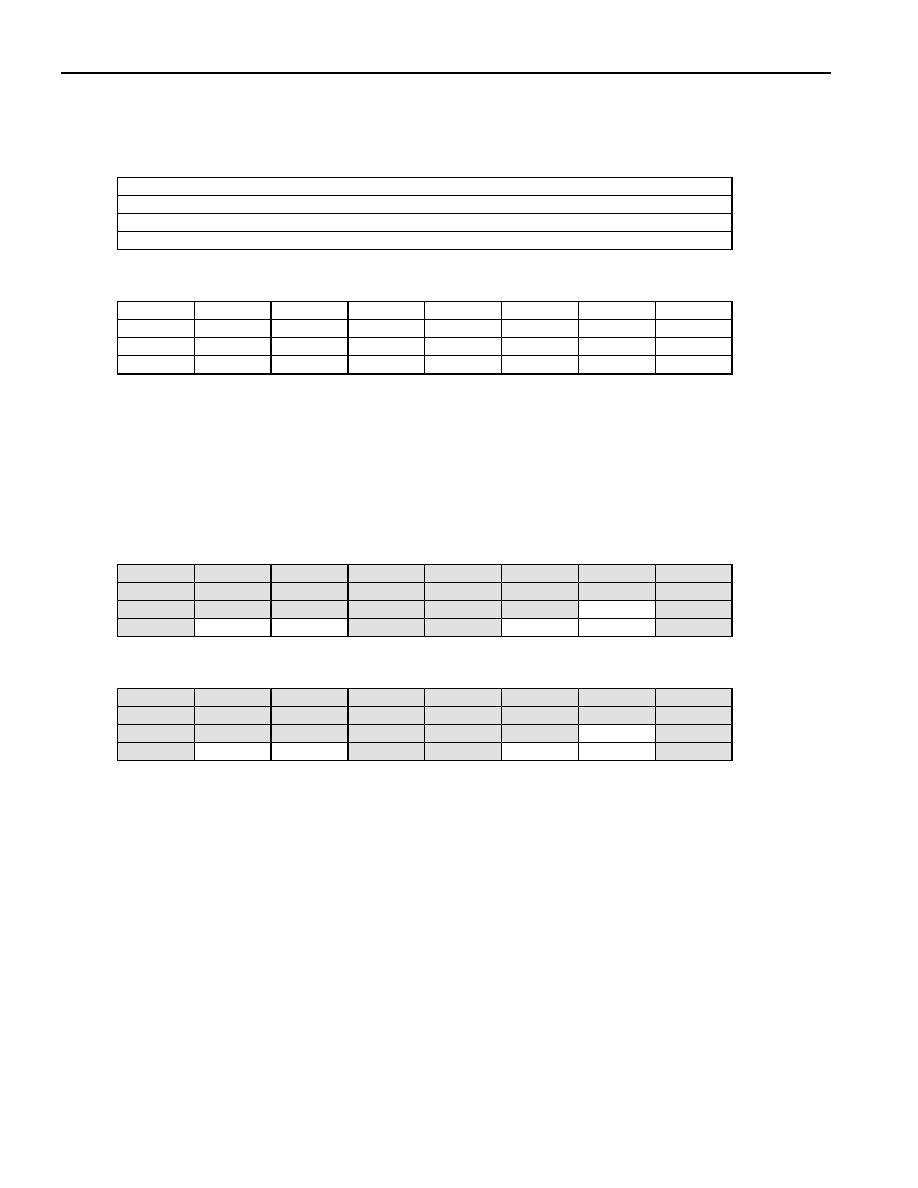

CSR Register:

Wake-Up Frame Filter

Register Address:

28h

Bit Names:

31

WUFD [31:24]

24

23

WUFD [23:16]

16

15

WUFD [15:8]

8

7

WUFD [7:0]

0

Reset State:

31

0

24

23

0

16

15

0

8

7

0

WUFD [31:0], Wake-Up Frame Filter Data [31:0]. These 32 bits are used to access the four available network

wake-up frame filters. Eight accesses to the wake-up frame filter register are needed to read or write all four wake-

up frame filters.

CSR Register:

Wake-Up Events Control and Status

Register Address:

2Ch

Bit Names:

31

—

24

23

—

16

15

—

GU

—

8

7

—

WUFF

MPF

—

WUFE

MPE

—

0

Reset State:

31

0

24

23

0

16

15

0

8

7

0

0*

0

*Power-on reset only. Unaffected by other reset sources.

GU, Global Unicast

0 = frames must pass the destination address filter as well as the wake-up frame filter criteria in order to generate a

wake-up event (default)

1 = frames must pass only the wake-up frame filter criteria to generate a wake-up event

WUFF, Wake-Up Frame Received Flag. This bit is set to logic 1 to indicate when a wake-up event was generated

due to the reception of a network wake-up frame. Application software must clear this flag by writing a 1 to this bit.

MPF, Magic Packet Received Flag. This bit is set to logic 1 to indicate when a wake-up event was generated due

to the reception of a Magic Packet. Application software must clear this flag by writing a 1 to this bit.

WUFE, Wake-Up Frame Enable. Setting this bit to logic 1 invokes sleep mode and allows the reception of network

wake-up frame to generate a wake-up event.

MPE, Magic Packet Enable. Setting this bit to logic 1 invokes sleep mode and allows the reception of a Magic

Packet to generate a wake-up event.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B43-IX-F1 | CONVERTER MOD DC/DC 24V 75W |

| DS89C450-ENL+ | IC MCU FLASH 64KB 33MHZ 44-TQFP |

| VE-B43-IW-F3 | CONVERTER MOD DC/DC 24V 100W |

| DS89C450-MNL+ | IC MCU FLASH 64KB 33MHZ 40-DIP |

| VE-B43-IW-F2 | CONVERTER MOD DC/DC 24V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS80C400-FNY+ | 功能描述:8位微控制器 -MCU Network MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| DS80C400-KIT | 功能描述:EVAL KIT FOR DS80C400 RoHS:否 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:- 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| DS80C400-KIT# | 功能描述:开发板和工具包 - 8051 RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

| DS80C410 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Network Microcontrollers with Ethernet and CAN |

| DS80C410_09 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Network Microcontrollers with Ethernet and CAN |

发布紧急采购,3分钟左右您将得到回复。