- 您现在的位置:买卖IC网 > PDF目录11784 > DS80C400-FNY+ (Maxim Integrated Products)IC MCU 75MHZ 16MB HP 100-LQFP PDF资料下载

参数资料

| 型号: | DS80C400-FNY+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 83/97页 |

| 文件大小: | 0K |

| 描述: | IC MCU 75MHZ 16MB HP 100-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 90 |

| 系列: | 80C |

| 核心处理器: | 8051 |

| 芯体尺寸: | 8-位 |

| 速度: | 75MHz |

| 连通性: | 1 线,CAN,EBI/EMI,以太网,SIO,UART/USART |

| 外围设备: | 电源故障复位,WDT |

| 输入/输出数: | 64 |

| 程序存储器容量: | 64KB(64K x 8) |

| 程序存储器类型: | ROM |

| RAM 容量: | 1K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 1.62 V ~ 3.6 V |

| 振荡器型: | 外部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 100-LQFP |

| 包装: | 托盘 |

| 配用: | DS80C400-KIT#-ND - EVAL KIT FOR DS80C400 |

| 其它名称: | DS80C400+FNY DS80C400+FNY+ DS80C400+FNY+-ND DS80C400+FNY-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页当前第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页

DS80C400 Network Microcontroller

84 of 97

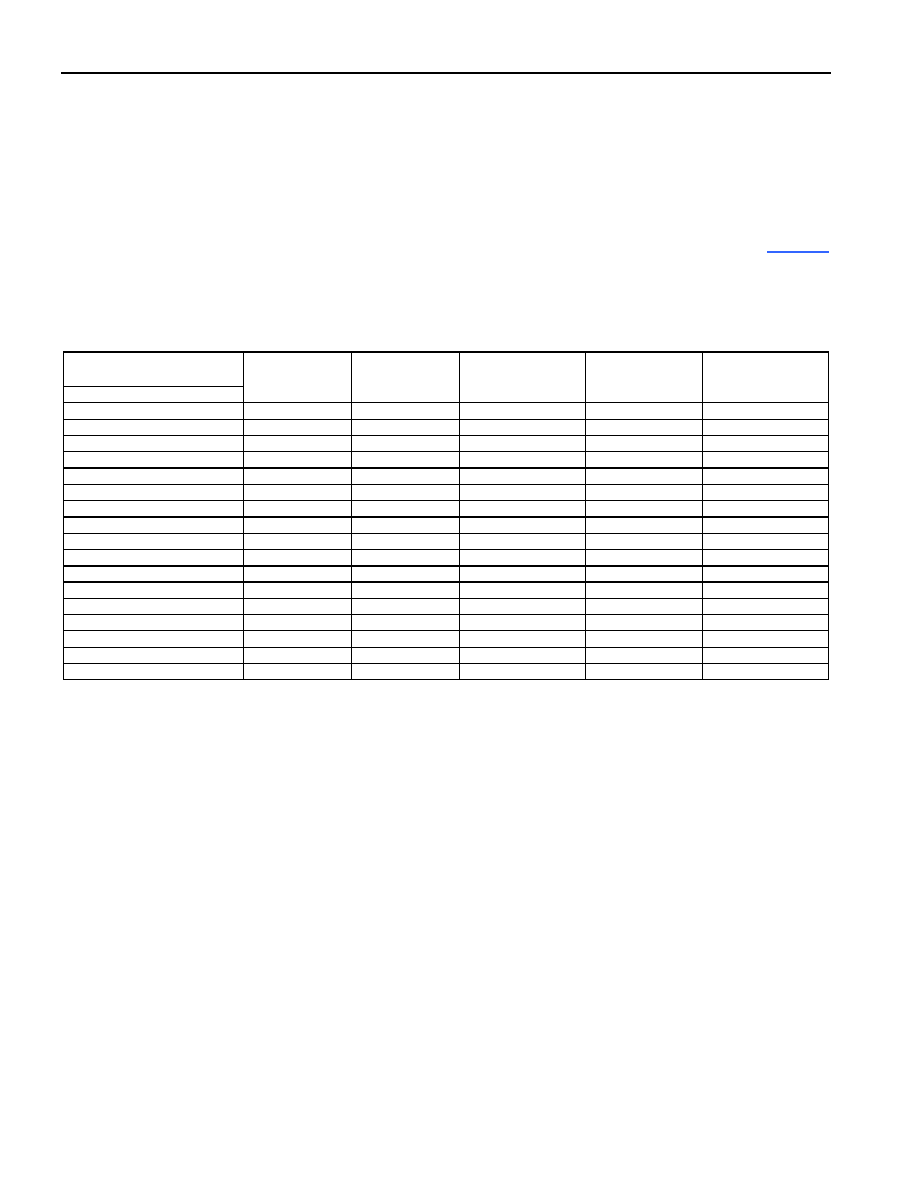

Clock Control

All 1-Wire timing patterns are generated using a base clock of 1.0MHz. To create this base clock frequency for the

1-Wire bus master, the microcontroller system clock must be internally divided down. The clock divisor internal

register implements bits to control this clock division and generation. The prescaler bits (PRE1:PRE0) divide the

microcontroller system clock by 1, 3, 5, or 7 for settings of 00b, 01b, 10b, and 11b respectively. The divider bits

(DIV2:DIV0) control the circuitry, which then divides the prescaler output clock by 1, 2, 4, 8, 16, 32, 64, or 128. The

CLK_EN bit (bit 7 of the clock divisor register) enables or disables the clock generation circuitry. Setting CLK_EN to

a logic 1 enables the clock generation circuitry while clearing the bit disables the clock generation circuitry. The

clock divisor register must be configured properly before any 1-Wire communication can take place. Table 23

shows the proper selections for the PRE1:PRE0 and DIV2:DIV0 register bits for a given microcontroller system

clock. Note that the clock generation circuitry requires that the microcontroller system clock be between 3.2MHz

and 75MHz, preferably with 50% duty cycle.

Table 23. Clock Divisor Register Settings

SYSTEM CLOCK

FREQUENCY (MHz)

DIVIDER

RATIO

DIV2:DIV0

DIVIDE BITS

SELECTION

PRE1:PRE0

PRESCALER

BITS

SELECTION

MIN

MAX

4.0

< 5.0

4

010

4

00

1

5.0

< 6.0

5

000

1

10

5

6.0

< 7.0

6

001

2

01

3

7.0

< 8.0

7

000

1

11

7

8.0

< 10.0

8

011

8

00

1

10.0

< 12.0

10

001

2

10

5

12.0

< 14.0

12

010

4

01

3

14.0

< 16.0

14

001

2

11

7

16.0

< 20.0

16

100

16

00

1

20.0

< 24.0

20

010

4

10

5

24.0

< 28.0

24

011

8

01

3

28.0

< 32.0

28

010

4

11

7

32.0

< 40.0

32

101

32

00

1

40.0

< 48.0

40

011

8

10

5

48.0

< 56.0

48

100

16

01

3

56.0

< 64.0

56

011

8

11

7

64.0

75.0

64

110

64

00

1

Transmitting and Receiving Data

All data transmitted and received by the 1-Wire bus master passes through the transmit/receive data buffer

(internal register address xxxxx001b). The data buffer is double-buffered with separate transmit and receive

buffers. Writing to the data buffer connects the transmit buffer to the data bus while reading connects the receive

buffer to the data bus.

The data buffer combination for the transmit interface is composed of the transmit buffer and transmit shift register.

Each of these registers has a flag that can be used as an interrupt source. The transmit buffer empty (TBE) flag is

set when the transmit buffer is empty and ready to accept a new byte of data from the user. As soon as the data

byte is written into the transmit buffer, TBE is cleared. The transmit shift register empty (TEMT) flag is set when the

shift register has no data and is ready to load a new data byte from the transmit buffer. When a byte of data is

transferred into the transmit shift register, TEMT is cleared and TBE becomes set.

To send a byte of data on the 1-Wire bus, the user writes the desired data to the transmit buffer. The data is moved

to the transmit shift register, where it is shifted serially onto the 1-Wire bus, least significant bit first. When the

transmit shift register is empty, new data is transferred from the transmit buffer (if available) and the serial process

repeats. Note that the 1-Wire protocol requires a reset before any bus communication.

The data buffer combination for the receive interface is composed of the receive buffer and the receive shift

register. The receive registers can also generate interrupts. The receive shift register full (RSRF) flag is set at the

start of data being shifted into the register, and is cleared when the receive shift register is empty. The receive

buffer full (RBF) flag is set when data is transferred from the receive shift register into the receive buffer and is

cleared after the CPU reads the register. If RBF is set, and another byte of data is received in the receive shift

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B43-IX-F1 | CONVERTER MOD DC/DC 24V 75W |

| DS89C450-ENL+ | IC MCU FLASH 64KB 33MHZ 44-TQFP |

| VE-B43-IW-F3 | CONVERTER MOD DC/DC 24V 100W |

| DS89C450-MNL+ | IC MCU FLASH 64KB 33MHZ 40-DIP |

| VE-B43-IW-F2 | CONVERTER MOD DC/DC 24V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS80C400-FNY+ | 功能描述:8位微控制器 -MCU Network MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| DS80C400-KIT | 功能描述:EVAL KIT FOR DS80C400 RoHS:否 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:- 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| DS80C400-KIT# | 功能描述:开发板和工具包 - 8051 RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

| DS80C410 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Network Microcontrollers with Ethernet and CAN |

| DS80C410_09 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Network Microcontrollers with Ethernet and CAN |

发布紧急采购,3分钟左右您将得到回复。