- 您现在的位置:买卖IC网 > PDF目录299030 > EP1K50FI256 (ALTERA CORP) LOADABLE PLD, PBGA256 PDF资料下载

参数资料

| 型号: | EP1K50FI256 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA256 |

| 封装: | 17 X 17 MM, 1 MM PITCH, FINE LINE, BGA-256 |

| 文件页数: | 46/84页 |

| 文件大小: | 2224K |

| 代理商: | EP1K50FI256 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

50

Altera Corporation

ACEX 1K Programmable Logic Family Data Sheet

Preliminary Information

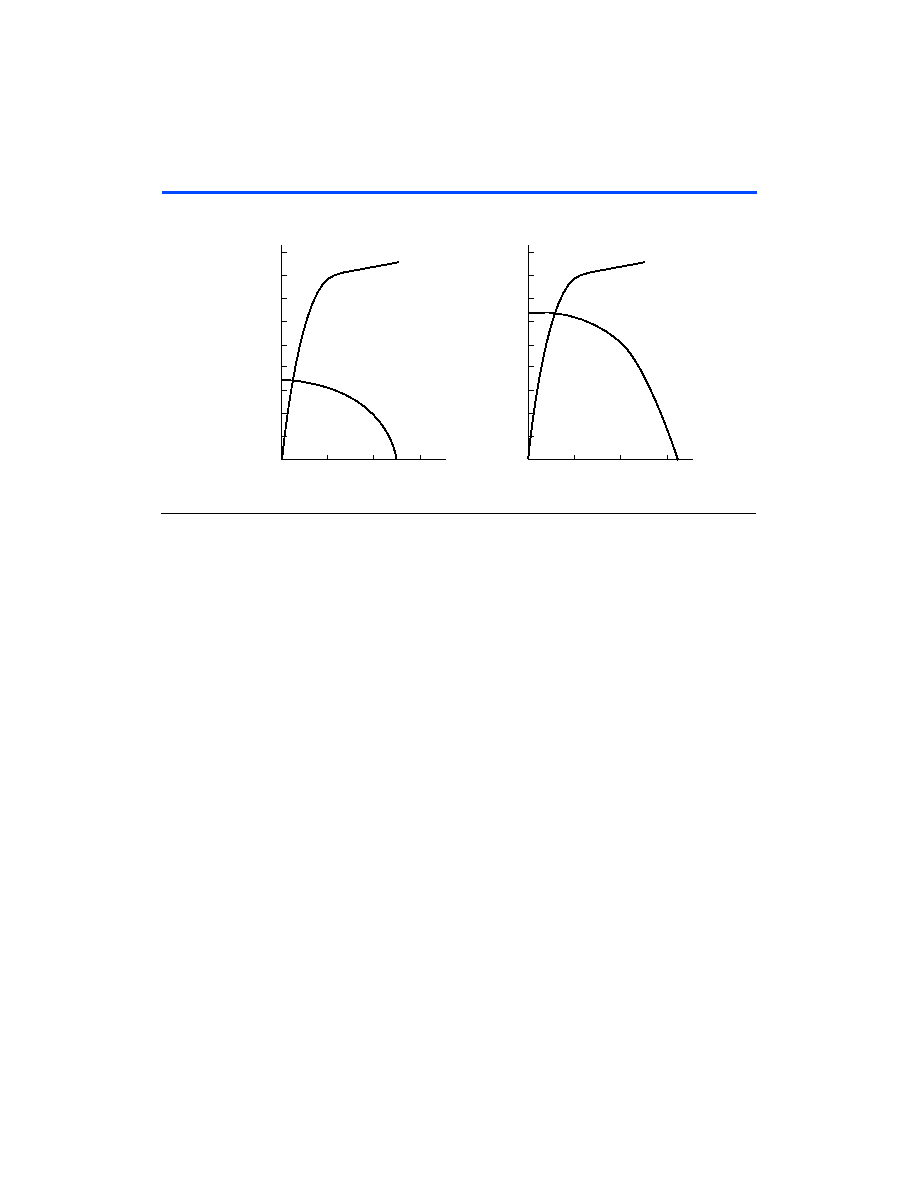

Figure 23. Output Drive Characteristics of ACEX 1K Devices

Timing Model

The continuous, high-performance FastTrack Interconnect routing

resources ensure accurate simulation and timing analysis as well as

predictable performance. This predictable performance contrasts with

that of FPGAs, which use a segmented connection scheme and, therefore,

have an unpredictable performance.

Device performance can be estimated by following the signal path from a

source, through the interconnect, to the destination. For example, the

registered performance between two LEs on the same row can be

calculated by adding the following parameters:

s

LE register clock-to-output delay (tCO)

s

Interconnect delay (tSAMEROW)

s

LE look-up table delay (tLUT)

s

LE register setup time (tSU)

The routing delay depends on the placement of the source and destination

LEs. A more complex registered path may involve multiple combinatorial

LEs between the source and destination LEs.

Timing simulation and delay prediction are available with the

MAX+PLUS II Simulator and Timing Analyzer, or with industry-

standard EDA tools. The Simulator offers both pre-synthesis functional

simulation to evaluate logic design accuracy and post-synthesis timing

simulation with 0.1-ns resolution. The Timing Analyzer provides point-

to-point timing delay information, setup and hold time analysis, and

device-wide performance analysis.

VO Output Voltage (V)

IOL

IOH

V

VCCINT = 2.5

VCCIO = 2.5

Room Temperature

V

VCCINT = 2.5

VCCIO = 3.3

Room Temperature

1

2

3

10

20

30

50

60

40

70

80

90

VO Output Voltage (V)

1

2

3

10

20

30

50

60

40

70

80

90

IOL

O

Typical I

Output

Current (mA)

O

Typical I

Output

Current (mA)

相关PDF资料 |

PDF描述 |

|---|---|

| EP1K50FI484 | LOADABLE PLD, PBGA484 |

| EP1K50QC208 | LOADABLE PLD, PQFP208 |

| EP1K50QI208 | LOADABLE PLD, PQFP208 |

| EP1K50TC144 | LOADABLE PLD, PQFP144 |

| EP1K50TI144 | LOADABLE PLD, PQFP144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP1K50FI256-1DX | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP1K50FI256-1F | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP1K50FI256-1P | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP1K50FI256-1X | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP1K50FI256-2 | 功能描述:FPGA - 现场可编程门阵列 FPGA - ACEX 1K 360 LABs 186 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。