- 您现在的位置:买卖IC网 > PDF目录299030 > EP20K100BC196-2 (ALTERA CORP) LOADABLE PLD, PBGA196 PDF资料下载

参数资料

| 型号: | EP20K100BC196-2 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA196 |

| 文件页数: | 38/68页 |

| 文件大小: | 975K |

| 代理商: | EP20K100BC196-2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

43

4317K–AVR–03/2013

AT90PWM2/3/2B/3B

Notes:

1. Only recommended with external crystal or resonator selected as clock source.

2. Only level interrupt.

8.6

Power Reduction Register

The Power Reduction Register, PRR, provides a method to stop the clock to individual peripher-

als to reduce power consumption. The current state of the peripheral is frozen and the I/O

registers can not be read or written. Resources used by the peripheral when stopping the clock

will remain occupied, hence the peripheral should in most cases be disabled before stopping the

clock. Waking up a module, which is done by clearing the bit in PRR, puts the module in the

same state as before shutdown.

A full predictible behaviour of a peripheral is not guaranteed during and after a cycle of stopping

and starting of its clock. So its recommended to stop a peripheral before stopping its clock with

PRR register.

Module shutdown can be used in Idle mode and Active mode to significantly reduce the overall

power consumption. In all other sleep modes, the clock is already stopped.

8.6.1

Power Reduction Register - PRR

Note:

PRPSC1 is not used on AT90PWM2/2B

Bit 7 - PRPSC2: Power Reduction PSC2

Writing a logic one to this bit reduces the consumption of the PSC2 by stopping the clock to this

module. When waking up the PSC2 again, the PSC2 should be re initialized to ensure proper

operation.

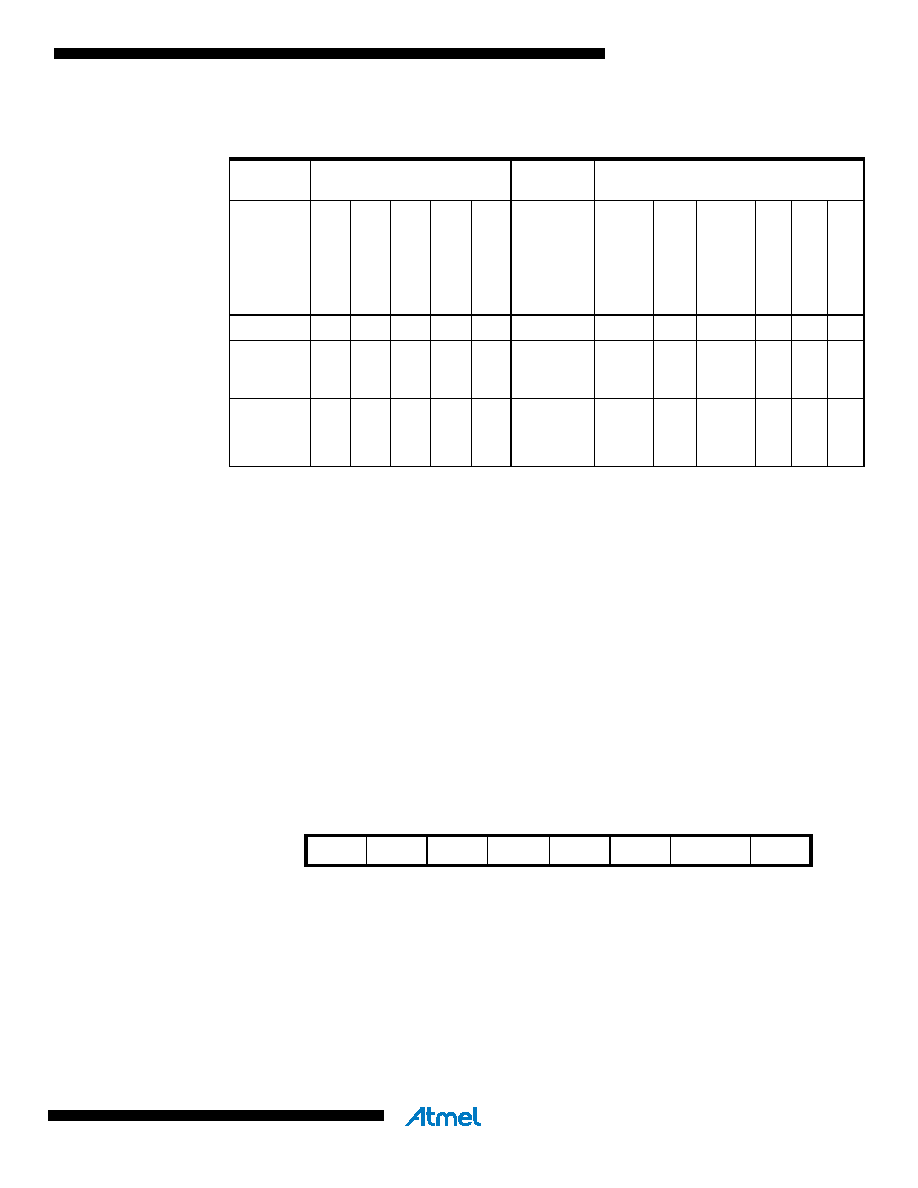

Table 8-2.

Active Clock Domains and Wake-up Sources in the Different Sleep Modes.

Active Clock Domains

Oscillator

s

Wake-up Sources

Sleep

Mode

clk

CPU

clk

FLASH

clk

IO

clk

ADC

clk

PLL

Ma

in

Clo

c

k

Sour

ce

Enab

led

INT

3

..

0

PSC

SPM/E

EPR

OM

Rea

d

y

ADC

WD

T

Ot

herI/

O

Idle

XXX

X

ADC

Noise

Reduction

XX

X

X(2)

XX

X

Power-

down

X(2)

XX

Standby(1)

XX(2)

X

Bit

7

6

543

2

1

0

PRPSC2

PRPSC1(

PRPSC0

PRTIM1

PRTIM0

PRSPI

PRUSART

PRADC

PRR

Read/Write

R/W

Initial Value

0

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100BC196-3 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-1 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-2 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-3 | LOADABLE PLD, PBGA196 |

| EP20K100BC324-1 | LOADABLE PLD, PBGA324 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100BC356-1 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BC356-1V | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP20K100BC356-2 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。