- 您现在的位置:买卖IC网 > PDF目录299030 > EP20K100BC196-2 (ALTERA CORP) LOADABLE PLD, PBGA196 PDF资料下载

参数资料

| 型号: | EP20K100BC196-2 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA196 |

| 文件页数: | 48/68页 |

| 文件大小: | 975K |

| 代理商: | EP20K100BC196-2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

52

4317K–AVR–03/2013

AT90PWM2/3/2B/3B

9.2

Watchdog Timer

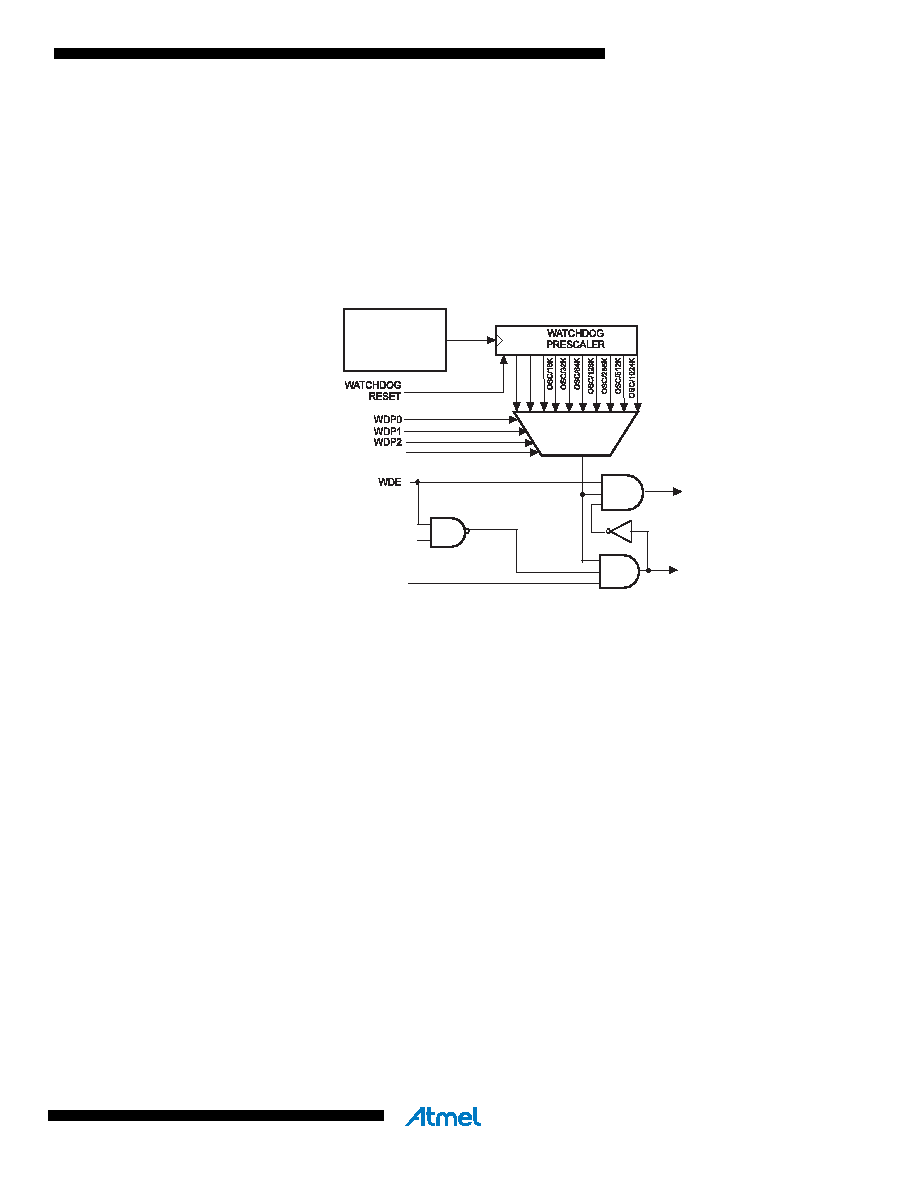

AT90PWM2/2B/3/3B has an Enhanced Watchdog Timer (WDT). The main features are:

Clocked from separate On-chip Oscillator

3 Operating modes

– Interrupt

– System Reset

– Interrupt and System Reset

Selectable Time-out period from 16ms to 8s

Possible Hardware fuse Watchdog always on (WDTON) for fail-safe mode

Figure 9-7.

Watchdog Timer

The Watchdog Timer (WDT) is a timer counting cycles of a separate on-chip 128 kHz oscillator.

The WDT gives an interrupt or a system reset when the counter reaches a given time-out value.

In normal operation mode, it is required that the system uses the WDR - Watchdog Timer Reset

- instruction to restart the counter before the time-out value is reached. If the system doesn't

restart the counter, an interrupt or system reset will be issued.

In Interrupt mode, the WDT gives an interrupt when the timer expires. This interrupt can be used

to wake the device from sleep-modes, and also as a general system timer. One example is to

limit the maximum time allowed for certain operations, giving an interrupt when the operation

has run longer than expected. In System Reset mode, the WDT gives a reset when the timer

expires. This is typically used to prevent system hang-up in case of runaway code. The third

mode, Interrupt and System Reset mode, combines the other two modes by first giving an inter-

rupt and then switch to System Reset mode. This mode will for instance allow a safe shutdown

by saving critical parameters before a system reset.

The “Watchdog Timer Always On” (WDTON) fuse, if programmed, will force the Watchdog Timer

to System Reset mode. With the fuse programmed the System Reset mode bit (WDE) and Inter-

rupt mode bit (WDIE) are locked to 1 and 0 respectively. To further ensure program security,

alterations to the Watchdog set-up must follow timed sequences. The sequence for clearing

WDE and changing time-out configuration is as follows:

1.

In the same operation, write a logic one to the Watchdog change enable bit (WDCE) and

WDE. A logic one must be written to WDE regardless of the previous value of the WDE

bit.

2.

Within the next four clock cycles, write the WDE and Watchdog prescaler bits (WDP) as

desired, but with the WDCE bit cleared. This must be done in one operation.

128 KHz

OSCILLATOR

MCU RESET

INTERRUPT

WDIE

WDIF

OSC/2K

OSC/4K

OSC/8K

WDP3

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100BC196-3 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-1 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-2 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-3 | LOADABLE PLD, PBGA196 |

| EP20K100BC324-1 | LOADABLE PLD, PBGA324 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100BC356-1 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BC356-1V | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP20K100BC356-2 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。