- 您现在的位置:买卖IC网 > PDF目录299030 > EP20K100BC196-2 (ALTERA CORP) LOADABLE PLD, PBGA196 PDF资料下载

参数资料

| 型号: | EP20K100BC196-2 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA196 |

| 文件页数: | 42/68页 |

| 文件大小: | 975K |

| 代理商: | EP20K100BC196-2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

47

4317K–AVR–03/2013

AT90PWM2/3/2B/3B

Notes:

1. Values are guidelines only..

2. The Power-on Reset will not work unless the supply voltage has been below VPOT (falling)

9.0.3

Power-on Reset

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detection level

is defined in Table 9-1. The POR is activated whenever V

CC is below the detection level. The

POR circuit can be used to trigger the start-up Reset, as well as to detect a failure in supply

voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the

Power-on Reset threshold voltage invokes the delay counter, which determines how long the

device is kept in RESET after V

CC rise. The RESET signal is activated again, without any delay,

when V

CC decreases below the detection level.

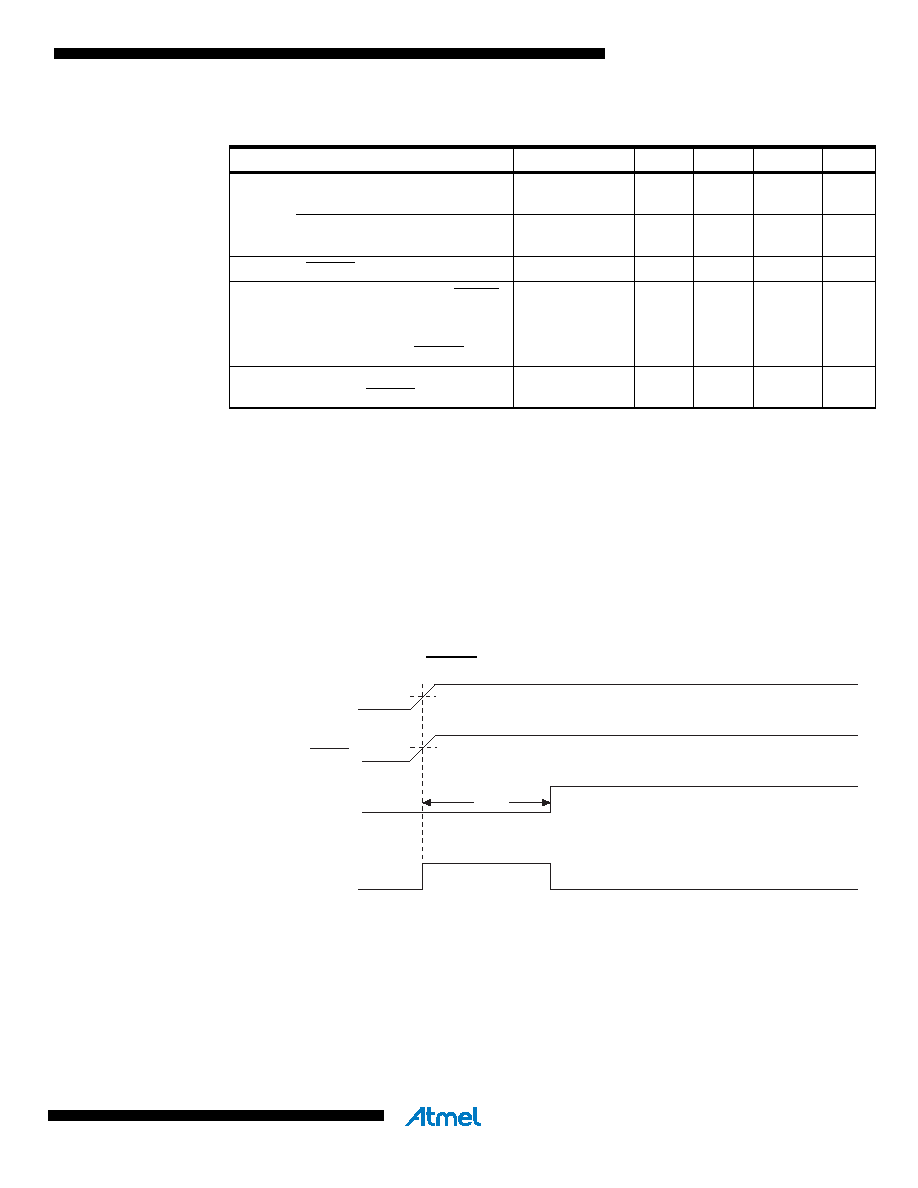

Figure 9-2.

MCU Start-up, RESET Tied to V

CC

Table 9-1.

Reset Characteristics(1)

Symbol

Parameter

Condition

Min.

Typ.

Max.

Units

VPOT

Power-on Reset Threshold

Voltage (rising)

1.4

2.3

V

Power-on Reset Threshold

Voltage (falling)(2)

1.3

2.3

V

VRST

RESET Pin Threshold Voltage

0.2Vcc

0.85Vcc

V

tRST

Minimum pulse width on RESET

Pin

400

ns

VPOR

VCC start voltage to ensure

internal Power-on RESET signal

-0.05

GND

+0.05

V

CCRR

VCC Rise Rate to ensure internal

Power-on RESET signal

0.3

V/ms

V

RESET

TIME-OUT

INTERNAL

RESET

t

TOUT

V

POT

V

RST

CC

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100BC196-3 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-1 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-2 | LOADABLE PLD, PBGA196 |

| EP20K100BI196-3 | LOADABLE PLD, PBGA196 |

| EP20K100BC324-1 | LOADABLE PLD, PBGA324 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100BC356-1 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BC356-1V | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP20K100BC356-2 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。