- 您现在的位置:买卖IC网 > PDF目录224000 > HYS72T128000EU-2.5-C2 (QIMONDA AG) 128M X 72 DDR DRAM MODULE, 0.4 ns, DMA240 PDF资料下载

参数资料

| 型号: | HYS72T128000EU-2.5-C2 |

| 厂商: | QIMONDA AG |

| 元件分类: | DRAM |

| 英文描述: | 128M X 72 DDR DRAM MODULE, 0.4 ns, DMA240 |

| 封装: | GREEN, UDIMM-240 |

| 文件页数: | 56/59页 |

| 文件大小: | 3071K |

| 代理商: | HYS72T128000EU-2.5-C2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页

HYS[64/72]T[128/256]0x0EU–[19F/1.9/25F/2.5/3S]–C2

Unbuffered DDR2 SDRAM Modules

Internet Data Sheet

Rev. 1.00, 2008-06

6

12032007-I9KE-FFWO

2

Pin Configurations

2.1

Pin Configurations

The pin configuration of the Unbuffered DDR2 SDRAM DIMM is listed by function in Table 5 (240 pins). The abbreviations used

in columns Pin and Buffer Type are explained in Table 6 and Table 7 respectively. The pin numbering is depicted in Figure 1

for non-ECC modules (

×64) and Figure 2 for ECC modules (×72).

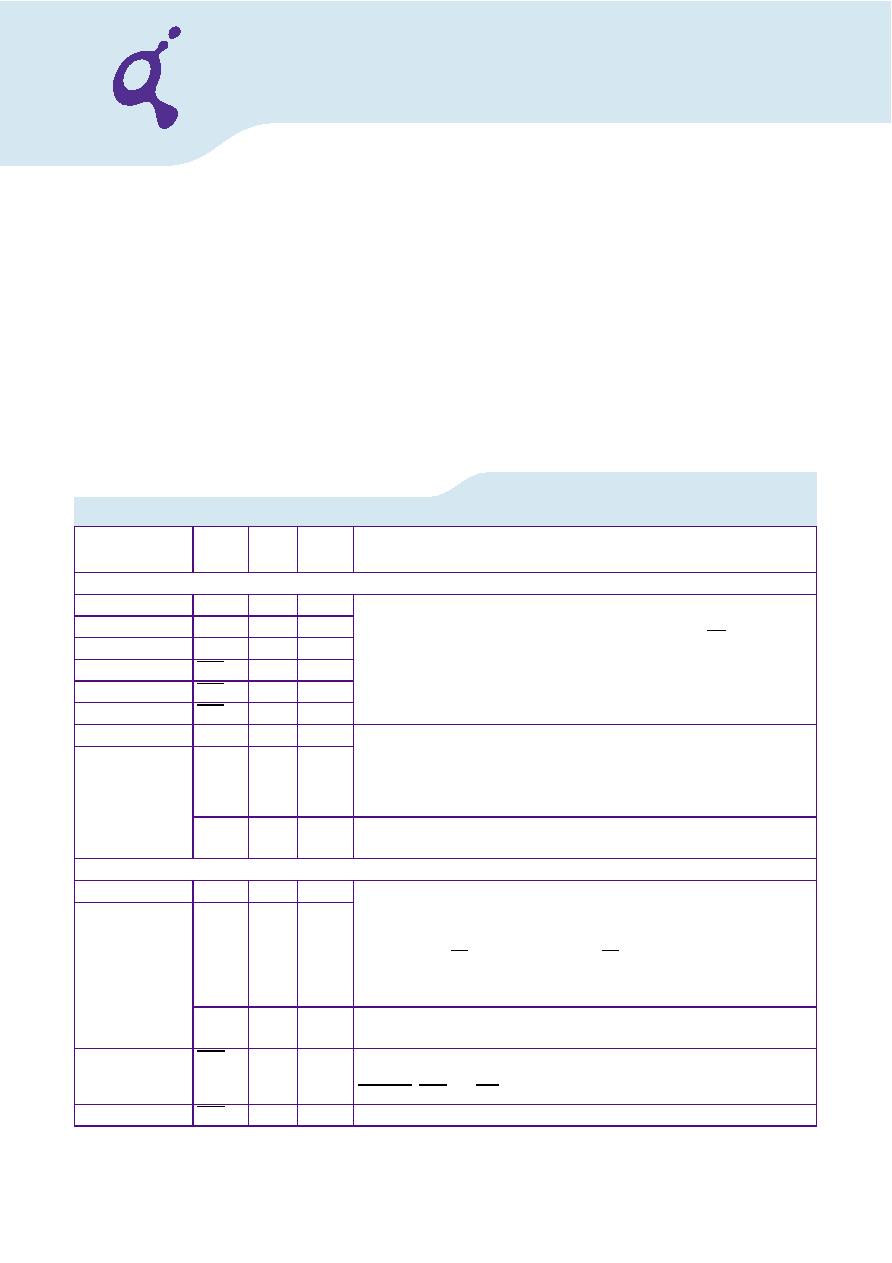

TABLE 5

Pin Configuration of UDIMM

Ball No.

Name

Pin

Type

Buffer

Type

Function

Clock Signals

185

CK0

I

SSTL

Clock Signals 2:0, Complement Clock Signals 2:0

The system clock inputs. All address and command lines are sampled on the

cross point of the rising edge of CK and the falling edge of CK. A Delay

Locked Loop (DLL) circuit is driven from the clock inputs and output timing for

read operations is synchronized to the input clock.

137

CK1

I

SSTL

220

CK2

I

SSTL

186

CK0

I

SSTL

138

CK1

I

SSTL

221

CK2

I

SSTL

52

CKE0

I

SSTL

Clock Enable Rank 1:0

Activates the DDR2 SDRAM CK signal when HIGH and deactivates the CK

signal when LOW. By deactivating the clocks, CKE LOW initiates the Power

Down Mode or the Self Refresh Mode.

Note: 2 Ranks module

171

CKE1

I

SSTL

NC

—

Not Connected

Note: 1 Rank module

Control Signals

193

S0

I

SSTL

Chip Select Rank 1:0

Enables the associated DDR2 SDRAM command decoder when LOW and

disables the command decoder when HIGH. When the command decoder is

disabled, new commands are ignored but previous operations continue. Rank

0 is selected by S0; Rank 1 is selected by S1. Ranks are also called "Physical

banks".

Note: 2 Ranks module

76

S1

I

SSTL

NC

—

Not Connected

Note: 1 Rank module

192

RAS

I

SSTL

Row Address Strobe

When sampled at the cross point of the rising edge of CK,and falling edge of

CK, RAS, CAS and WE define the operation to be executed by the SDRAM.

74

CAS

I

SSTL

Column Address Strobe

相关PDF资料 |

PDF描述 |

|---|---|

| HYS72T64000EP-3.7-B2 | 64M X 72 DDR DRAM MODULE, DMA240 |

| HZ20-1 | 19.25 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-35 |

| HZ6B1L | 5.65 V, 0.4 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-35 |

| HZ9.1CP | 9.65 V, 1 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-41 |

| HZB6.8MWA | 6.8 V, 0.2 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HYS72T128000GR | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:DDR2 Registered Memory Modules |

| HYS72T128000GR-37-A | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:DDR2 Registered Memory Modules |

| HYS72T128000GR-5-A | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:DDR2 Registered Memory Modules |

| HYS72T128000HP | 制造商:QIMONDA 制造商全称:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T128000HP-2.5-B | 制造商:QIMONDA 制造商全称:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

发布紧急采购,3分钟左右您将得到回复。