- 您现在的位置:买卖IC网 > PDF目录67683 > IBM25PPC750CX-CP40-3T 32-BIT, 466 MHz, RISC PROCESSOR, PBGA256 PDF资料下载

参数资料

| 型号: | IBM25PPC750CX-CP40-3T |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 466 MHz, RISC PROCESSOR, PBGA256 |

| 封装: | PLASTIC, BGA-256 |

| 文件页数: | 8/43页 |

| 文件大小: | 509K |

| 代理商: | IBM25PPC750CX-CP40-3T |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页

PowerPC 750CX RISC Microprocessor Datasheet

Page 16

Version 1.2

Jun 20, 2001

5.3

60X Bus Input AC Specications

Table 7 provides the 60X bus input AC timing specications for the PowerPC 750CX as dened in Figure 3 and

Figure 3 provides the input timing diagram for the PowerPC 750CX.

Table 7: 60X Bus Input Timing Specications1,6,8

See Table 2 on page 12 for operating conditions.

Num

Characteristic

1.8V Mode

2.5V Mode

Unit

Notes

Min

Max.

Min.

Max.

10a

Address/Data/Transfer attribute inputs valid to SYSCLK (input

setup)

1.4

—

1.4

—

ns

2

10b

All other inputs valid to SYSCLK (input setup)

1.4

—

1.4

—

ns

3

10c

Mode select input setup to HRESET (QACK)

8—8—

tsysclk

4,5,7

10d

TS to SYSCLK (input setup)

1.6

—

1.6

—

10e

DBWO to SYSCLK (input setup)

2.1

—

2.1

—

11a

SYSCLK to inputs invalid (input hold)

1.2

—

1.2

—

ns

2

11b

HRESET to mode select input hold (QACK)

0

—

0

—

ns

4,7

Note:

1. Input specifications are measured from the midpoint voltage (0.9V) of the signal in question to the midpoint voltage of the rising edge of the input

SYSCLK. Input and output timings are measured at the pin (see Figure 3).

2. Address/Data Transfer Attribute inputs are composed of all bidirectional and input signals except those listed in Note 3.

3. All other signal inputs are composed of the following: TA, QACK, and ARTRY.

4. The setup and hold time is with respect to the rising edge of HRESET (see Figure 4 on page 17).

5. tSYSCLK, is the period of the external clock (SYSCLK) in nanoseconds (ns). The numbers given in the table must be multiplied by the period of SYSCLK

to compute the actual time duration (in ns) of the parameter in question.

6. These values are guaranteed by design, and are not tested.

7. This specification is for configuration mode select only. Also note that the HRESET must be held asserted for a minimum of 255 bus clocks after the

PLL relock time during the power-on reset sequence.

8. These timings are valid for processor frequencies up to 466MHz. 500MHz timing behavior and characterization is being evaluated at this time.

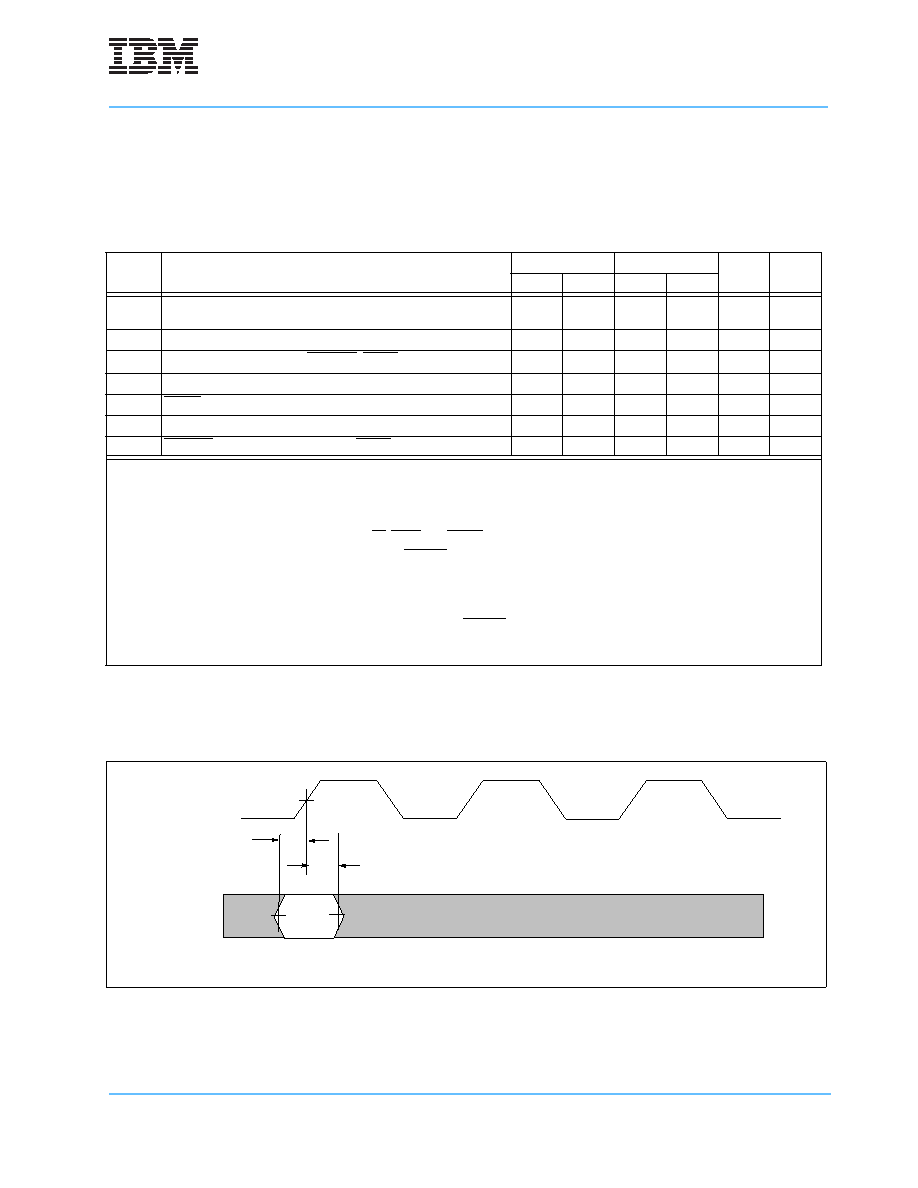

Figure 3. Input Timing Diagram

VM

SYSCLK

ALL INPUTS

VM = Midpoint Voltage (0.8V for SYSCLK, 0.9V for all other I/O)

10b

10a

11a

VM

10d

10e

相关PDF资料 |

PDF描述 |

|---|---|

| IBM25PPC750CXEFP10-3T | RISC PROCESSOR, PBGA256 |

| IBM25PPC750CXEJP7012T | 32-BIT, 600 MHz, RISC PROCESSOR, PBGA256 |

| IBM25PPC750CXEJP5523T | 32-BIT, 533 MHz, RISC PROCESSOR, PBGA256 |

| IBM25PPC750CXEJQ5012T | 32-BIT, 500 MHz, RISC PROCESSOR, PBGA256 |

| IBM25PPC750CXEJQ4012T | 32-BIT, 466 MHz, RISC PROCESSOR, PBGA256 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IBM25PPC750CXEJP2013T | 制造商:IBM Microelectronics 功能描述:MPU 750XX RISC 32BIT 0.18UM 400MHZ 1.8V/2.5V 256BGA - Trays 制造商:IBM 功能描述:IBM IBM25PPC750CXEJP2013T Co-Processors |

| IBM25PPC750CXEJP5512T | 制造商:IBM 功能描述: |

| IBM25PPC750CXEJP7012T | 制造商:IBM Microelectronics 功能描述:MPU 750XX RISC 32BIT 0.18UM 600MHZ 1.8V/2.5V 256BGA - Trays 制造商:IBM 功能描述:IBM IBM25PPC750CXEJP7012T Co-Processors |

| IBM25PPC750CXEJP7013T | 制造商:IBM 功能描述:IBMIBM25PPC750CXEJP7013T OEM EOL151207 |

| IBM25PPC750FL-GR0123V | 制造商:IBM 功能描述:MPU 750XX RISC 32BIT - Trays |

发布紧急采购,3分钟左右您将得到回复。