- 您现在的位置:买卖IC网 > PDF目录239729 > IBM25PPC750GXEBB2532T 32-BIT, 800 MHz, RISC PROCESSOR, CBGA292 PDF资料下载

参数资料

| 型号: | IBM25PPC750GXEBB2532T |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 800 MHz, RISC PROCESSOR, CBGA292 |

| 封装: | 21 X 21 MM, 1 MM PITCH, CERAMIC, BGA-292 |

| 文件页数: | 43/74页 |

| 文件大小: | 1054K |

| 代理商: | IBM25PPC750GXEBB2532T |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页

Datasheet

IBM PowerPC 750GX RISC Microprocessor

DD1.X

System Design Information

Page 48 of 73

750GX_ds_body.fm SA14-2765-02

September 2, 2005

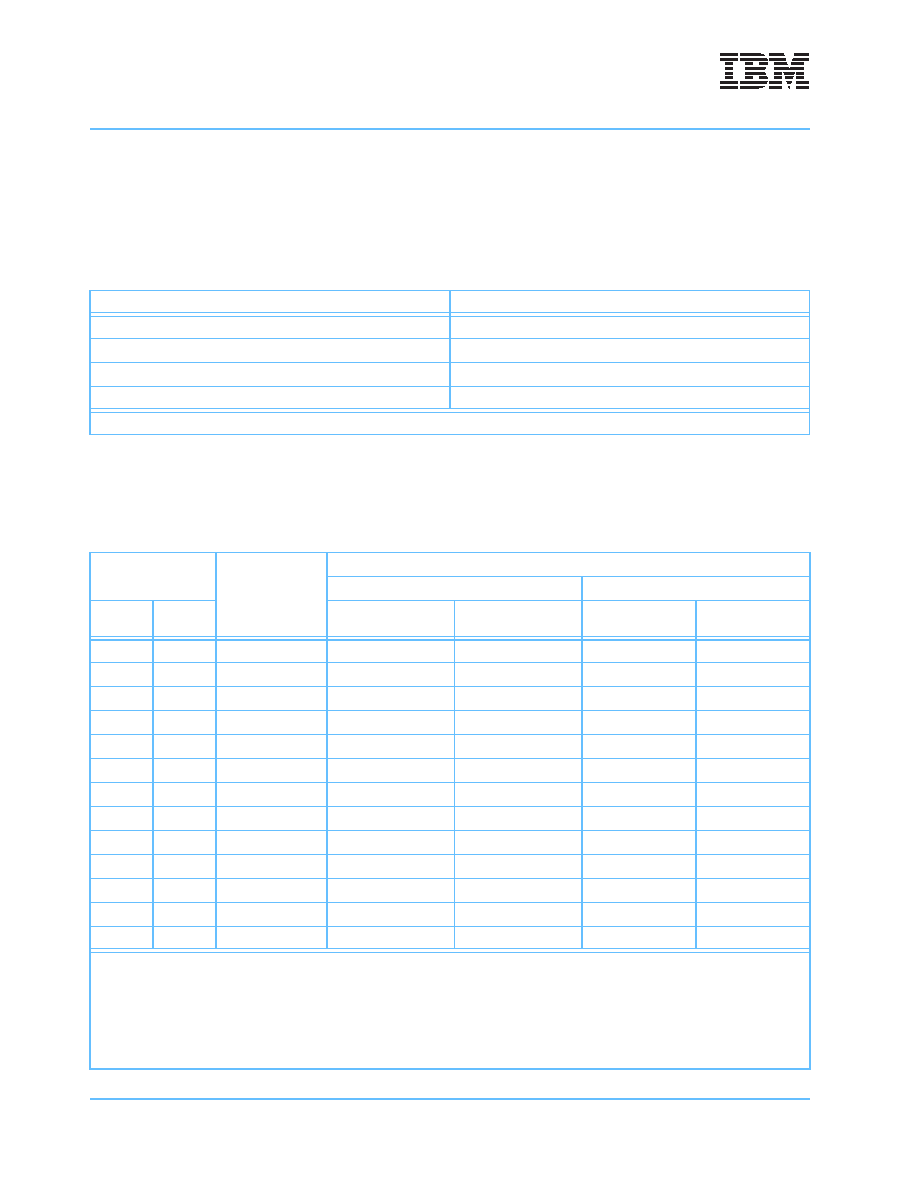

5.2.3 PLL_RNG[0:1] Definitions for Dual PLL Operation

The dual PLLs on the 750GX are configured by the PLL_CFG[0:4] and PLL_RNG[0:1] signals. For a given

SYSCLK (bus) frequency, the PLL configuration signals set the internal CPU and voltage controlled oscillator

(VCO) frequency of operation. The 750GX PLL range configuration for dual PLL operation is shown in the

following table.

5.2.4 PLL Configuration

Table 5-2 shows the PLL configuration for the 750GX for nominal frequencies.

Table 5-1. PLL_RNG[0:1] Definitions for Dual PLL Operation

PLL_RNG[0:1]

PLL Frequency Range

00 (default)

600 MHz–900 MHz

01 (fast)

900 MHz–1.0 GHz

10 (slow)

500 MHz–600 MHz

11 (reserved)

Reserved

Note: PLL_RNG bit settings are valid for a VDD range of 1.4 V–1.55 V and a temperature range of -40°C–105°C.

Table 5-2. 750GX Microprocessor PLL Configuration

PLL_CFG [0:4]

Processor to Bus

Frequency Ratio

(PTBFR)

Frequency Range Supported by VCO Having an Example Range of...

SYSCLK1 (MHz)

Core (MHz)

Binary

Decimal

Minimum

(SYSCLKMIN)

Maximum

(SYSCLKMAX)

Minimum

(Core FrequencyMIN)

Maximum

(Core FrequencyMAX)

00000

0

Off2

N/A

Off

00001

1

Off2

N/A

Off

00010

2

PLL Bypass3

N/A

00011

3

PLL Bypass3

N/A

00100

4

2×4

N/A

00101

5

2.5×4

200

500

00110

6

3×4

167

200

500

600

00111

7

3.5×4

143

200

500

700

01000

8

4×

125

200

500

800

01001

9

4.5×

111

200

500

900

01010

10

5×

100

200

500

1000

01011

11

5.5×

91

182

500

1000

01100

12

6×

83

166

500

1000

Notes:

1. The SYSCLK frequency equals the core frequency divided by the processor-to-bus frequency ratio (PTBFR).

2. In clock-off mode, no clocking occurs inside the 750GX regardless of the SYSCLK input.

3. In PLL-bypass mode, the SYSCLK input signal clocks the internal processor directly, the PLL is disabled, and the bus mode is set

for 1:1 mode operation. This mode is intended for factory use only.

The AC timing specifications given in the document do not apply in PLL-bypass mode.

4. The 2×–3.5× processor-to-bus ratios are currently not supported when miss-under-miss is enabled (HID0(14) = '1').

相关PDF资料 |

PDF描述 |

|---|---|

| ICS843023AGT | 320 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| IRFR9121 | 5.9 A, 80 V, 0.6 ohm, P-CHANNEL, Si, POWER, MOSFET, TO-252AA |

| IM1P-67202AV-25 | 1K X 9 OTHER FIFO, 25 ns, CDIP28 |

| IM3P-67202AL-45 | 1K X 9 OTHER FIFO, 45 ns, PDIP28 |

| IMDP-67202AL-25 | 1K X 9 OTHER FIFO, 25 ns, CDFP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IBM25PPC750GXEBB2562T | 制造商:IBM 功能描述: |

| IBM25PPC750GXEBB2563T | 制造商:IBM 功能描述: |

| IBM25PPC750GXECB2563T | 制造商:IBM 功能描述: |

| IBM25PPC750GXECB2H33T | 制造商:IBM 功能描述: |

| IBM25PPC750GXECB5H42V | 制造商:IBM 功能描述:POLARIS 1.2 ? 21CBGA GRE2 ? HALFMODE 933MH - Trays |

发布紧急采购,3分钟左右您将得到回复。