- 您现在的位置:买卖IC网 > PDF目录239729 > IBM25PPC750GXEBB2532T 32-BIT, 800 MHz, RISC PROCESSOR, CBGA292 PDF资料下载

参数资料

| 型号: | IBM25PPC750GXEBB2532T |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 800 MHz, RISC PROCESSOR, CBGA292 |

| 封装: | 21 X 21 MM, 1 MM PITCH, CERAMIC, BGA-292 |

| 文件页数: | 46/74页 |

| 文件大小: | 1054K |

| 代理商: | IBM25PPC750GXEBB2532T |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页

Datasheet

IBM PowerPC 750GX RISC Microprocessor

DD1.X

System Design Information

Page 50 of 73

750GX_ds_body.fm SA14-2765-02

September 2, 2005

5.3 PLL Power Supply Filtering

The 750GX microprocessor has two separate AVDD signals (A1VDD and A2VDD), which provide power to the

clock generation PLL.

Most designs are expected to use a single PLL configuration mode throughout the application. These types of

designs should use the default PLL (PLL0), filtering its respective supply, A1VDD. The A2VDD supply signal

should be grounded through a 100

resistor, as shown in Figure 5-1 on page 51.

For designs planning to optimize power savings through dynamic switching between dual PLL circuits, it is

recommended, though not required, that each AVDD have a separate voltage input and filter circuit. This

optional circuit is also shown.

To ensure stability of the internal clock, the power supplied to the AVDD input signals should be filtered using

a circuit similar to the one shown in Figure 5-1 on page 51. The circuit should be placed as close as possible

to the AVDD pin to ensure it filters out as much noise as possible.

For descriptions of the sample PLL power supply filtering circuits, see Table 5-3.

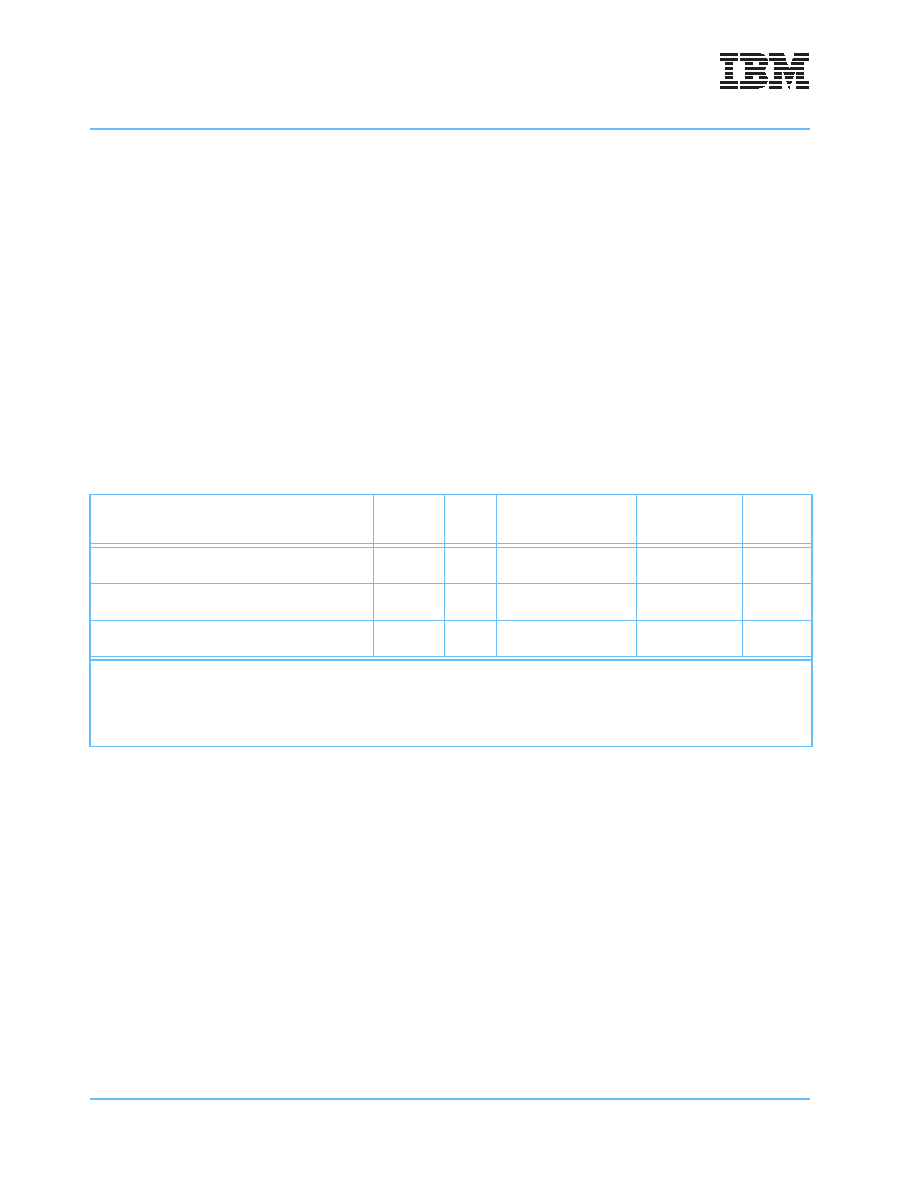

Table 5-3. Sample PLL Power Supply Filtering Circuits

Circuit Description

Number of

Filtering

Circuits

Ferrite

Beads

Circuit Figure

Recommended

Circuit Design

Notes

Single PLL circuit configuration that uses the A1VDD

and ties the A2VDD pin to GND.

11

Yes

Single PLL circuit configuration that uses both the

A1VDD and the A2VDD pins and a single ferrite bead.

11

Optional

Dual PLL configuration that uses a separate circuit

for the A1VDD pin and for the A2VDD pin.

22

Yes

Notes:

1. Optional configurations are supported, though not recommended.

2. This circuit design can be used with the dual PLL feature enabled, though optimum power savings may not be realized.

For additional information, see Figure 5-3, Dual PLL Power Supply Filter Circuits, on page 52.

3. This circuit design can be used with the dual PLL feature enabled to optimize power savings.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS843023AGT | 320 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| IRFR9121 | 5.9 A, 80 V, 0.6 ohm, P-CHANNEL, Si, POWER, MOSFET, TO-252AA |

| IM1P-67202AV-25 | 1K X 9 OTHER FIFO, 25 ns, CDIP28 |

| IM3P-67202AL-45 | 1K X 9 OTHER FIFO, 45 ns, PDIP28 |

| IMDP-67202AL-25 | 1K X 9 OTHER FIFO, 25 ns, CDFP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IBM25PPC750GXEBB2562T | 制造商:IBM 功能描述: |

| IBM25PPC750GXEBB2563T | 制造商:IBM 功能描述: |

| IBM25PPC750GXECB2563T | 制造商:IBM 功能描述: |

| IBM25PPC750GXECB2H33T | 制造商:IBM 功能描述: |

| IBM25PPC750GXECB5H42V | 制造商:IBM 功能描述:POLARIS 1.2 ? 21CBGA GRE2 ? HALFMODE 933MH - Trays |

发布紧急采购,3分钟左右您将得到回复。