- 您现在的位置:买卖IC网 > PDF目录239729 > IBM25PPC750GXEBB2532T 32-BIT, 800 MHz, RISC PROCESSOR, CBGA292 PDF资料下载

参数资料

| 型号: | IBM25PPC750GXEBB2532T |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 800 MHz, RISC PROCESSOR, CBGA292 |

| 封装: | 21 X 21 MM, 1 MM PITCH, CERAMIC, BGA-292 |

| 文件页数: | 68/74页 |

| 文件大小: | 1054K |

| 代理商: | IBM25PPC750GXEBB2532T |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页当前第68页第69页第70页第71页第72页第73页第74页

Datasheet

IBM PowerPC 750GX RISC Microprocessor

DD1.X

System Design Information

Page 70 of 73

750GX_ds_body.fm SA14-2765-02

September 2, 2005

5.9.3 I/O Voltage Mode Selection

Selection between 1.8 V, 2.5 V, or 3.3 V I/O modes is accomplished by using the BVSEL and L1_TSTCLK

pins:

If BVSEL = 1 and L1_TSTCLK = 0, then the 3.3 V mode is enabled.

If BVSEL = 1 and L1_TSTCLK = 1, then the 2.5 V mode is enabled.

If BVSEL = 0 and L1_TSTCLK = 1, then the 1.8 V mode is enabled.

Note: Do not set BVSEL = 0 and L1_TSTCLK = 0 since it yields an invalid mode.

5.9.4 QACK Signal Implementation for Selected Features

5.9.4.1 Precharge Duration Selection and Application

An extended precharge feature is available for the signals ABB, DBB, and ARTRY in situations where the

loading and net topology of these signals requires a longer precharge duration for the signals to attain a valid

level.

This feature has not been fully tested and should not be necessary in a properly designed system, even at

200 MHz. System designers should assume standard precharge as the default selection, with an option to

use extended precharge.

The bus signals, ABB, DBB, and ARTRY, require a precharge to the inactive state (bus high) before going to

tristate. The precharge duration in standard precharge mode is approximately one half cycle, and should be

used for systems with point-to-point topologies. Extended precharge mode increases the precharge duration

to one cycle. This increase may be required for bus speeds approaching 200 MHz when bus loading is high.

QACK in a logical high state at the transition of HRESET from asserted to negated enables standard pre-

charge mode in the 750GX. QACK in a logical low state at the transition of HRESET from asserted to negated

enables extended pre-charge mode in the 750GX.

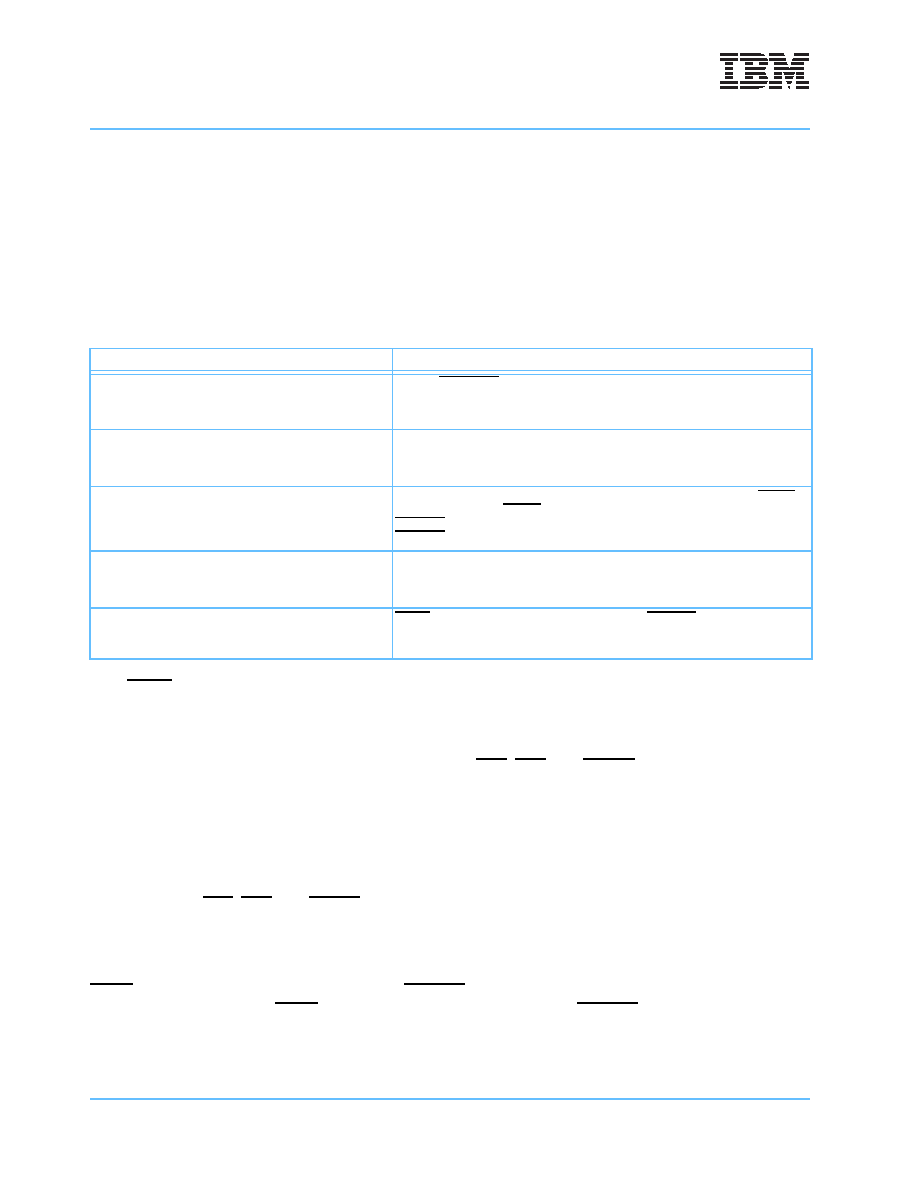

Table 5-10. Summary of Mode Select

Mode

750GX

32-bit mode

Sample TLBISYNC to select

High = 64-bit mode

Low = 32-bit mode

Data retry mode

Selects DRTRY mode.

0 at HRESET transition

No DRTRY mode

1 at HRESET transition

DRTRY mode

Factory usage modes

Factory usage modes are selected by sensing the data bus disable (DBDIS),

data bus write-only (DBWO), and L2_TSTCLK pins at the transition of

HRESET from low to high. These pins should be held inactive (high) at the

HRESET transition for normal machine operation.

I/O mode selection

3.3 V

±165 mV (BVSEL = 1, L1_TSTCLK = 0) or

2.5 V

±125 mV (BVSEL = 1, L1_TSTCLK = 1) or

1.8 V

±100 mV (BVSEL = 0, L1_TSTCLK = 1)

Standard/extended precharge mode

QACK in a logical high state at the transition of HRESET from asserted to

negated enables standard precharge mode, the recommended default. See

Section 5.9.4.1 for details.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS843023AGT | 320 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| IRFR9121 | 5.9 A, 80 V, 0.6 ohm, P-CHANNEL, Si, POWER, MOSFET, TO-252AA |

| IM1P-67202AV-25 | 1K X 9 OTHER FIFO, 25 ns, CDIP28 |

| IM3P-67202AL-45 | 1K X 9 OTHER FIFO, 45 ns, PDIP28 |

| IMDP-67202AL-25 | 1K X 9 OTHER FIFO, 25 ns, CDFP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IBM25PPC750GXEBB2562T | 制造商:IBM 功能描述: |

| IBM25PPC750GXEBB2563T | 制造商:IBM 功能描述: |

| IBM25PPC750GXECB2563T | 制造商:IBM 功能描述: |

| IBM25PPC750GXECB2H33T | 制造商:IBM 功能描述: |

| IBM25PPC750GXECB5H42V | 制造商:IBM 功能描述:POLARIS 1.2 ? 21CBGA GRE2 ? HALFMODE 933MH - Trays |

发布紧急采购,3分钟左右您将得到回复。