参数资料

| 型号: | IP-PCIE/8 |

| 厂商: | Altera |

| 文件页数: | 86/256页 |

| 文件大小: | 0K |

| 描述: | IP PCI EXPRESS, X8 |

| 标准包装: | 1 |

| 系列: | * |

| 类型: | MegaCore |

| 功能: | PCI Express 编译器,8 倍链路宽度 |

| 许可证: | 初始许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页当前第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页第226页第227页第228页第229页第230页第231页第232页第233页第234页第235页第236页第237页第238页第239页第240页第241页第242页第243页第244页第245页第246页第247页第248页第249页第250页第251页第252页第253页第254页第255页第256页

�� �

�

�

�Signals�

�Table� 3–23.� Standard� Data� Phase� Signals� (Part� 2� of� 2)�

�Signal�

�tx_data� n� [63:0]�

��I�

�I/O�

�Description�

�Transmit� data� bus.� This� signal� transfers� data� from� the� application� interface� to� the�

�link.� It� is� 2� DWORDS� wide� and� is� naturally� aligned� with� the� address� in� one� of� two�

�ways,� depending� on� bit� 2� of� the� transaction� layer� packet� address,� which� is� located�

�on� bit� 2� or� 34� of� the� tx_desc� (depending� on� the� 3� or� 4� DWORDS� transaction�

�layer� packet� header� bit� 125� of� the� tx_desc� signal).�

�tx_desc[2]� (64-bit� address)� set� to� 0:� The� first� DWORD� is� located� on�

�●�

�tx_data[31:0]� .�

�tx_desc[34]� (32-bit� address)� set� to� 0:� The� first� DWORD� is� located� on� bits�

�●�

�tx_data[31:0]� .�

�tx_desc[2]� (64-bit� address)� set� to� 1:� The� first� DWORD� is� located� on� bits�

�●�

�tx_data[63:32]� .�

�tx_desc[34]� (32-bit� address)� set� to� 1:� The� first� DWORD� is� located� on� bits�

�●�

�tx_data[63:32]� .�

�This� natural� alignment� allows� you� to� connect� the� tx_data[63:0]� directly� to� a�

�64-bit� data� path� aligned� on� a� QWORD� address� (in� the� little� endian� convention).�

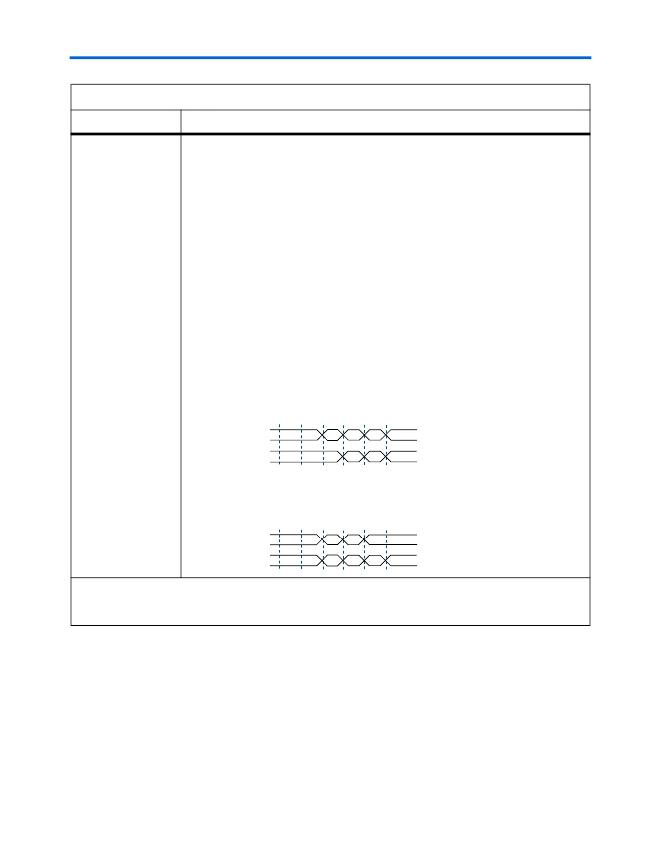

�Bit� 2� is� set� to� 1� (5� DWORDS� transaction).�

�Clock� Cycles�

�tx_data[63:32]�

�tx_data[31:0]�

�1�

�X�

�X�

�2�

�3�

�DW� 0�

�4�

�DW� 2�

�DW� 1�

�5�

�DW� 4�

�DW� 3�

�6�

�X�

�X�

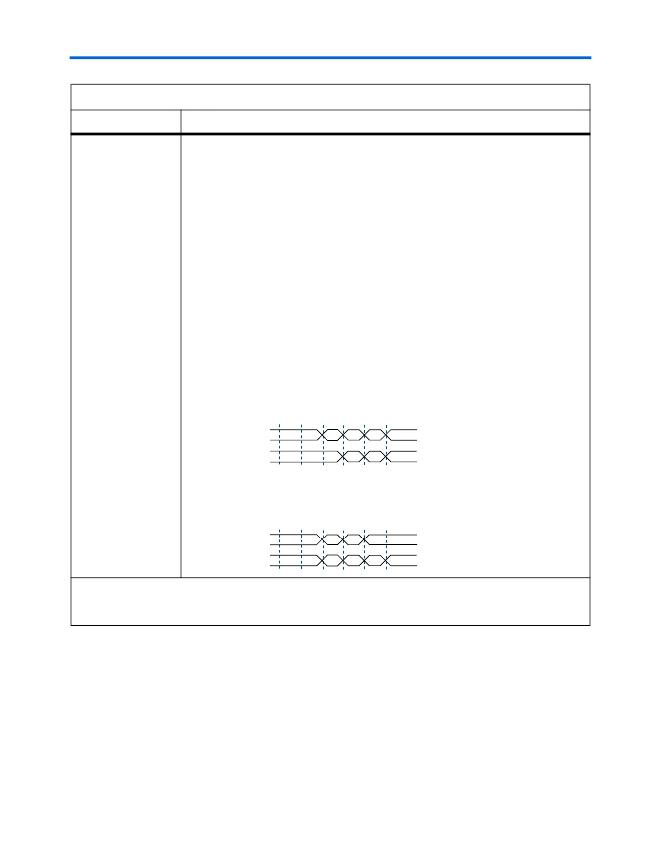

�Bit� 2� is� set� to� 0� (5� DWORDS� transaction).�

�Clock� Cycles�

�tx_data[63:32]�

�1�

�X�

�2�

�3�

�DW� 1�

�4�

�DW� 3�

�5�

�6�

�X�

�tx_data[31:0]�

�X�

�DW� 0�

�DW� 2�

�DW� 4�

�X�

��(1)� where� n� is� the� virtual� channel� number;� For� x1� and� x4,� n� can� be� 0� -� 3�

�(2)� For� x8,� n� can� be� 0� or� 1�

��3–48� PCI� Express� Compiler� Version� 6.1�

�PCI� Express� Compiler� User� Guide�

�Altera� Corporation�

�December� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| IP-POSPHY4 | IP POS-PHY L4 |

| IP-RIOPHY | IP RAPID I/O |

| IP-RLDRAMII | IP RLDRAM II CONTROLLER |

| IP-RSDEC | IP REED-SOLOMON DECODER |

| IP-SDI | IP VIDEO INTERFACE - SDI |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPPOEINJ1295 | 制造商:Speco Technologies 功能描述:PoE Injector - 12.95W |

| IPPOEINJ25 | 制造商:Speco 功能描述:POE INJECTOR - 25W UP TO 325FT |

| IPPOERPT | 制造商:Speco 功能描述:POE-LAN REPEATER POWER AND DATA UP TO 1000FT |

| IPPOESPL1295 | 制造商:Speco 功能描述:POE SPLITTER - 12.95WUP TO 325FT |

| IPPOESPL25 | 制造商:Speco 功能描述:POE SPLITTER - 25W UP TO 325FT |

发布紧急采购,3分钟左右您将得到回复。