- 您现在的位置:买卖IC网 > PDF目录16742 > ISPPAC-POWR1208-01TN44I (Lattice Semiconductor Corporation)IC ISP POWER MGR ANLG/LOG 44TQFP PDF资料下载

参数资料

| 型号: | ISPPAC-POWR1208-01TN44I |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 22/35页 |

| 文件大小: | 0K |

| 描述: | IC ISP POWER MGR ANLG/LOG 44TQFP |

| 标准包装: | 160 |

| 系列: | ispPAC® |

| 应用: | 电源监控器,序列发生器 |

| 输入电压: | 0 V ~ 6 V |

| 电源电压: | 2.7 V ~ 5.5 V |

| 电流 - 电源: | 10mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LQFP |

| 供应商设备封装: | 44-TQFP(10x10) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

�� �

�

Lattice� Semiconductor�

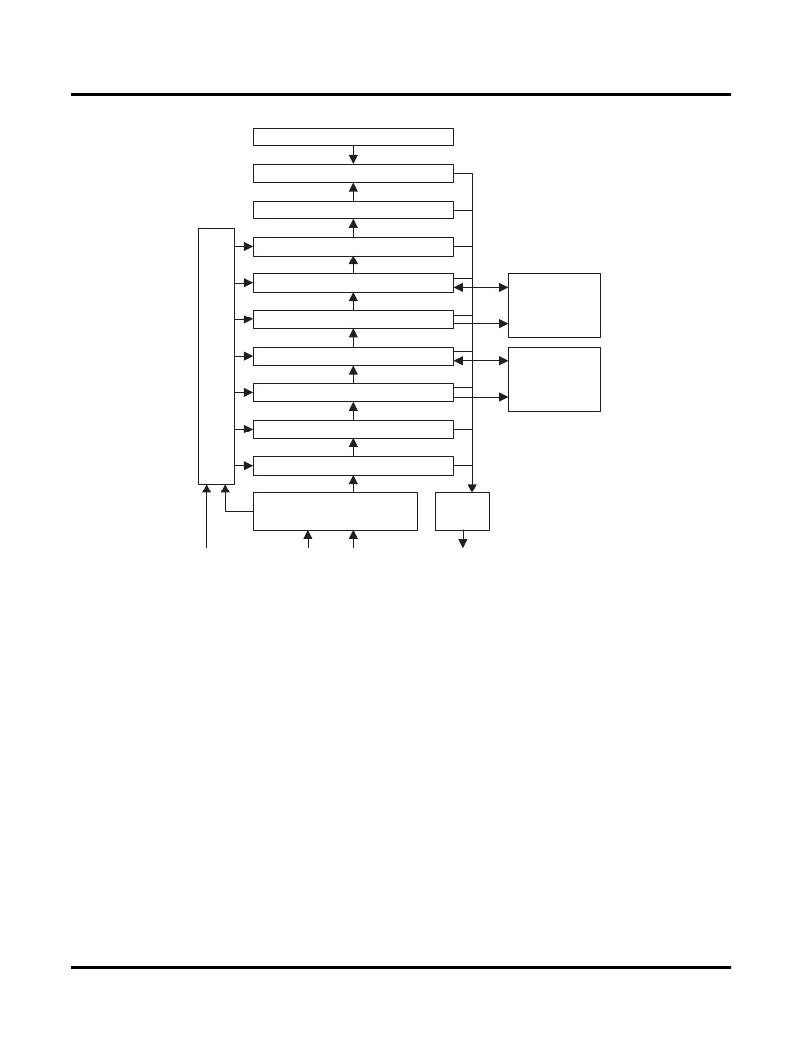

�Figure� 1-10.� TAP� Registers�

�ANALOG� COMPARATOR� ARRAY� (12� bits)�

�STATUS� REGISTER� (12� bits)�

�IDCODE� REGISTER� (32� bits)�

�UES� REGISTER� (16� bits)�

�CFG� REGISTER� (41� bits)�

�CFG� ADDRESS� REGISTER� (4� bits)�

�PLD� DATA� REGISTER� (81� bits)�

�PLD� ADDRESS� REGISTER� (75� bits)�

�INSTRUCTION� REGISTER� (6� bits)�

�BYPASS� REGISTER� (1� bit)�

�TEST� ACCESS� PORT�

�(TAP)� LOGIC�

�OUTPUT�

�LATCH�

�ispPAC-POWR1208� Data� Sheet�

�ANALOG�

�CONFIGURATION�

�E� 2� NON-VOLATILE�

�MEMORY�

�(164� bits)�

�PLD�

�AND� /� ARCH�

�E� 2� NON-VOLATILE�

�MEMORY�

�(6075� bits)�

�TDI�

�TCK�

�TMS�

�TDO�

�TAP� Controller� Speci?cs�

�The� TAP� is� controlled� by� the� Test� Clock� (TCK)� and� Test� Mode� Select� (TMS)� inputs.� These� inputs� determine� whether�

�an� Instruction� Register� or� Data� Register� operation� is� performed.� Driven� by� the� TCK� input,� the� TAP� consists� of� a�

�small� 16-state� controller.� In� a� given� state,� the� controller� responds� according� to� the� level� on� the� TMS� input� as� shown�

�in� Figure� 1-11.� Test� Data� In� (TDI)� and� TMS� are� latched� on� the� rising� edge� of� TCK,� with� Test� Data� Out� (TDO)� becom-�

�ing� valid� on� the� falling� edge� of� TCK.� There� are� six� steady� states� within� the� controller:� Test-Logic-Reset,� Run-Test/�

�Idle,� Shift-Data-Register,� Pause-Data-Register,� Shift-Instruction-Register,� and� Pause-Instruction-Register.� But�

�there� is� only� one� steady� state� for� the� condition� when� TMS� is� set� high:� the� Test-Logic-Reset� state.� This� allows� a�

�reset� of� the� test� logic� within� ?ve� TCKs� or� less� by� keeping� the� TMS� input� high.� Test-Logic-Reset� is� the� power-on�

�default� state.�

�When� the� correct� logic� sequence� is� applied� to� the� TMS� and� TCK� inputs,� the� TAP� will� exit� the� Test-Logic-Reset� state�

�and� move� to� the� desired� state.� The� next� state� after� Test-Logic-Reset� is� Run-Test/Idle.� Until� a� data� or� instruction�

�scan� is� performed,� no� action� will� occur� in� Run-Test/Idle� (steady� state� =� idle).� After� Run-Test/Idle,� either� a� data� or�

�instruction� scan� is� performed.� The� states� of� the� Data� and� Instruction� Register� blocks� are� identical� to� each� other� dif-�

�fering� only� in� their� entry� points.� When� either� block� is� entered,� the� ?rst� action� is� a� capture� operation.� For� the� Data�

�Registers,� the� Capture-DR� state� is� very� simple;� it� captures� (parallel� loads)� data� onto� the� selected� serial� data� path�

�(previously� chosen� with� the� appropriate� instruction).� For� the� Instruction� Register,� the� Capture-IR� state� will� always�

�load� the� IDCODE� instruction.� It� will� always� enable� the� ID� Register� for� readout� if� no� other� instruction� is� loaded� prior�

�to� a� Shift-DR� operation.� This,� in� conjunction� with� mandated� bit� codes,� allows� a� “blind”� interrogation� of� any� device� in�

�a� compliant� IEEE� 1149.1� serial� chain.�

�1-21�

�相关PDF资料 |

PDF描述 |

|---|---|

| ES1000-NO.4-B7-X-75MM | HEAT SHRINK TUBING |

| EBM36DCTS | CONN EDGECARD 72POS DIP .156 SLD |

| FSLBOT | KIT TOWER MECH BOARD |

| SN65LVDS31-33EVM | EVAL MOD FOR SN65LVDS31/33 |

| 4426R-3 | INDUCTOR AIR CORE 8.0NH SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISPPAC-POWR1208-01TN44I7R | 制造商:Lattice Semiconductor Corporation 功能描述: |

| ISPPAC-POWR1208P1 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:In-System Programmable Power Supply Sequencing Controller and Precision Monitor |

| ISPPACPOWR1208P101T44I | 制造商:Lattice Semiconductor Corporation 功能描述: |

| ISPPAC-POWR1208P1-01T44I | 功能描述:监控电路 PROGRAMMABLE PWR SUPPLY CONTR RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

| ISPPAC-POWR1208P1-01TN44I | 功能描述:监控电路 PROGRAMMABLE PWR SUPPLY CONTR RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。