- 您现在的位置:买卖IC网 > PDF目录16742 > ISPPAC-POWR1208-01TN44I (Lattice Semiconductor Corporation)IC ISP POWER MGR ANLG/LOG 44TQFP PDF资料下载

参数资料

| 型号: | ISPPAC-POWR1208-01TN44I |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 31/35页 |

| 文件大小: | 0K |

| 描述: | IC ISP POWER MGR ANLG/LOG 44TQFP |

| 标准包装: | 160 |

| 系列: | ispPAC® |

| 应用: | 电源监控器,序列发生器 |

| 输入电压: | 0 V ~ 6 V |

| 电源电压: | 2.7 V ~ 5.5 V |

| 电流 - 电源: | 10mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LQFP |

| 供应商设备封装: | 44-TQFP(10x10) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页

�� �

�

Lattice� Semiconductor�

�ispPAC-POWR1208� Data� Sheet�

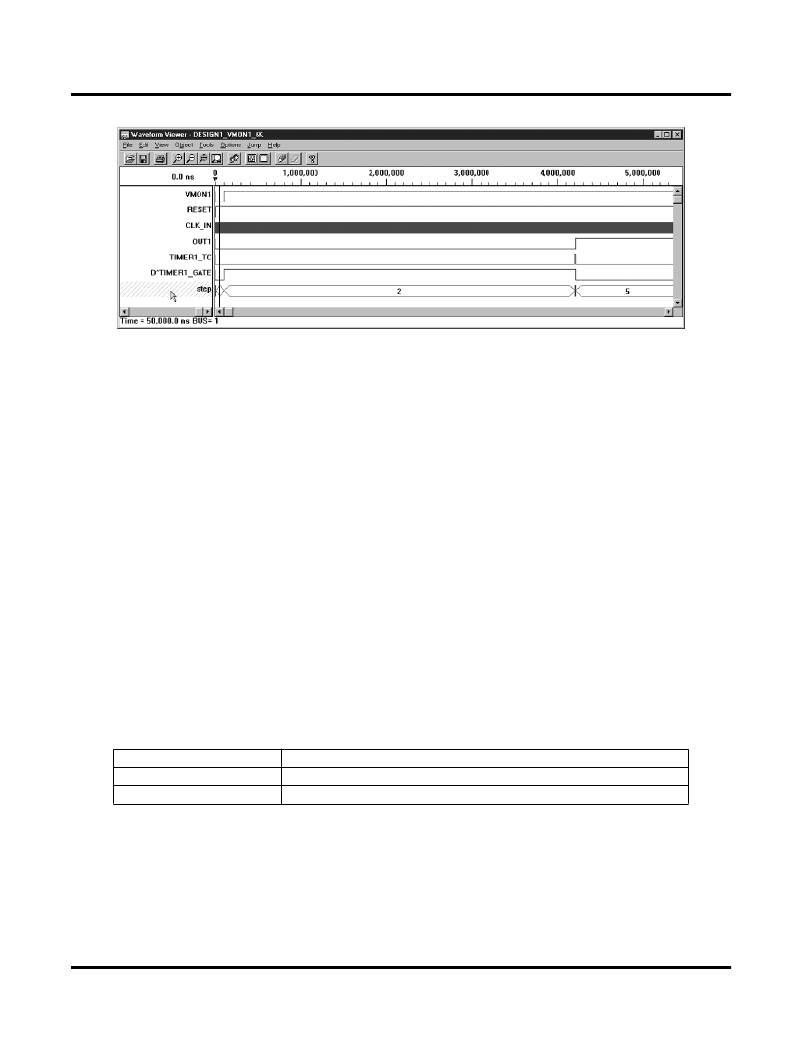

�Figure� 1-19.� PAC-Designer� Functional� Simulation� Screen�

�In-System� Programming�

�The� ispPAC-POWR1208� is� an� in-system� programmable� device.� This� is� accomplished� by� integrating� all� E� 2� CMOS�

�con?guration� memory� and� control� logic� on-chip.� Programming� is� performed� through� a� 4-wire,� IEEE� 1149.1� compli-�

�ant� serial� JTAG� interface.� Once� a� device� is� programmed,� all� con?guration� information� is� stored� on-chip,� in� non-vol-�

�atile� E� 2� CMOS� memory� cells.� The� speci?cs� of� the� IEEE� 1149.1� serial� interface� and� all� ispPAC-POWR1208�

�instructions� are� described� in� the� JTAG� interface� section� of� this� data� sheet.�

�User� Electronic� Signature�

�The� User� Electronic� Signature� (UES),� allows� the� designer� to� include� identi?cation� bits� or� serial� numbers� inside� the�

�device,� stored� in� E� 2� CMOS� memory.� The� ispPAC-POWR1208� contains� 16� UES� bits� that� can� be� con?gured� by� the�

�user� to� store� unique� data� such� as� ID� codes,� revision� numbers� or� inventory� control� codes.�

�Electronic� Security�

�An� Electronic� Security� Fuse� (ESF)� bit� is� provided� to� prevent� unauthorized� readout� of� the� E� 2� CMOS� bit� pattern.� Once�

�programmed,� this� cell� prevents� further� access� to� the� functional� user� bits� in� the� device.� This� cell� can� only� be� erased�

�by� reprogramming� the� device;� this� way� the� original� con?guration� cannot� be� examined� or� copied� once� programmed.�

�Usage� of� this� feature� is� optional.�

�Production� Programming� Support�

�Once� a� ?nal� con?guration� is� determined,� an� ASCII� format� JEDEC� ?le� can� be� created� using� the� PAC-Designer� soft-�

�ware.� Devices� can� then� be� ordered� through� the� usual� supply� channels� with� the� user’s� speci?c� con?guration� already�

�preloaded� into� the� devices.� By� virtue� of� its� standard� interface,� compatibility� is� maintained� with� existing� production�

�programming� equipment,� giving� customers� a� wide� degree� of� freedom� and� ?exibility� in� production� planning.�

�Part� Number�

�PAC-SYSTEM� POWR1208�

�ispPAC-POWR1208-EV�

�Description�

�Complete� system� kit,� evaluation� board,� ispDOWNLOAD� Cable� and� software�

�Evaluation� board� only,� with� components,� fully� assembled�

�Evaluation� Fixture�

�The� ispPAC-POWR1208� Design� Kit� includes� an� engineering� prototype� board� that� can� be� connected� to� the� parallel�

�port� of� a� PC� using� a� Lattice� ispDOWNLOAD� cable.� It� demonstrates� proper� layout� techniques� for� the� ispPAC-�

�POWR1208� and� can� be� used� in� real� time� to� check� circuit� operation� as� part� of� the� design� process.� LEDs� are� sup-�

�plied� to� debug� designs� without� involving� test� equipment.� Input� and� output� connections� as� well� as� a� “breadboard”�

�circuit� area� are� provided� to� speed� debugging� of� the� circuit.� The� board� includes� an� area� for� prototyping� other� circuits�

�1-30�

�相关PDF资料 |

PDF描述 |

|---|---|

| ES1000-NO.4-B7-X-75MM | HEAT SHRINK TUBING |

| EBM36DCTS | CONN EDGECARD 72POS DIP .156 SLD |

| FSLBOT | KIT TOWER MECH BOARD |

| SN65LVDS31-33EVM | EVAL MOD FOR SN65LVDS31/33 |

| 4426R-3 | INDUCTOR AIR CORE 8.0NH SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISPPAC-POWR1208-01TN44I7R | 制造商:Lattice Semiconductor Corporation 功能描述: |

| ISPPAC-POWR1208P1 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:In-System Programmable Power Supply Sequencing Controller and Precision Monitor |

| ISPPACPOWR1208P101T44I | 制造商:Lattice Semiconductor Corporation 功能描述: |

| ISPPAC-POWR1208P1-01T44I | 功能描述:监控电路 PROGRAMMABLE PWR SUPPLY CONTR RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

| ISPPAC-POWR1208P1-01TN44I | 功能描述:监控电路 PROGRAMMABLE PWR SUPPLY CONTR RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。