- 您现在的位置:买卖IC网 > PDF目录16742 > ISPPAC-POWR1208-01TN44I (Lattice Semiconductor Corporation)IC ISP POWER MGR ANLG/LOG 44TQFP PDF资料下载

参数资料

| 型号: | ISPPAC-POWR1208-01TN44I |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 30/35页 |

| 文件大小: | 0K |

| 描述: | IC ISP POWER MGR ANLG/LOG 44TQFP |

| 标准包装: | 160 |

| 系列: | ispPAC® |

| 应用: | 电源监控器,序列发生器 |

| 输入电压: | 0 V ~ 6 V |

| 电源电压: | 2.7 V ~ 5.5 V |

| 电流 - 电源: | 10mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LQFP |

| 供应商设备封装: | 44-TQFP(10x10) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页

�� �

�

Lattice� Semiconductor�

�ispPAC-POWR1208� Data� Sheet�

�FET� Drivers� :� Allows� the� user� to� de?ne� ramp� rates� by� controlling� the� current� driven� to� the� gate� of� the� external� FETs.�

�Maximum� voltage� levels� and� pin� names� are� also� set� using� this� functional� block.� The� four� FET� driver� outputs�

�HVOUT1-4� can� also� be� con?gured� as� open-drain� digital� logic� outputs.�

�Logic� Outputs� :� These� pins� are� con?gured� and� assigned� in� the� Logic� Output� Functional� Block.� The� four� digital� out-�

�puts� are� open-drain� and� require� a� pull-up� resistor.�

�Internal� Clock� :� The� internal� clock� con?guration� and� clock� prescaler� values� are� user-programmable,� as� well� as� the�

�four� internal� programmable� timers� used� for� sequence� delay.�

�User� Electronic� Signature� (UES)� :� Stores� 16� bits� of� ID� or� board� information� in� non-volatile� E� 2� CMOS.�

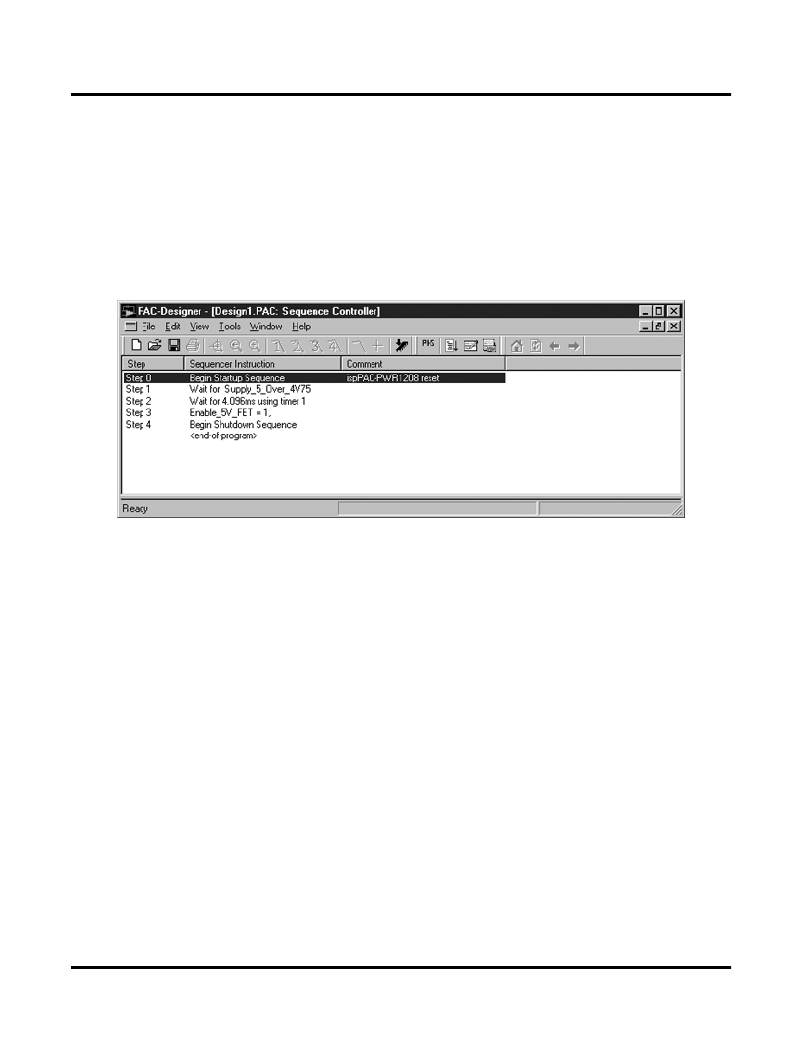

�Figure� 1-18.� PAC-Designer� LogiBuilder� Screen�

�Programming� of� the� ispPAC-POWR1208� is� accomplished� using� the� Lattice� ispDOWNLOAD� Cable.� This� cable� con-�

�nects� to� the� parallel� port� of� a� PC� and� is� driven� through� the� PAC-Designer� software.� The� software� controls� the� JTAG�

�TAP� interface� and� shifts� in� the� JEDEC� data� bits� that� set� the� con?guration� of� all� the� analog� and� digital� circuitry� that�

�the� user� has� de?ned� during� the� design� process.�

�Power� to� the� device� must� be� set� at� 3.0V� to� 5.5V� during� programming,� once� the� programming� steps� have� been� com-�

�pleted,� the� power� supply� to� the� ispPAC-POWR1208� can� be� set� from� 2.5V� to� 5V.� Once� programmed,� the� on-chip�

�non-volatile� E� 2� CMOS� bits� hold� the� entire� design� con?guration� for� the� digital� circuits,� analog� circuits� and� trip� points�

�for� comparators� etc.� Upon� powering� the� device� up,� the� non-volatile� E� 2� CMOS� bits� control� the� device� con?guration.� If�

�design� changes� need� to� be� made� such� as� adjusting� comparator� trip� points� or� changes� to� the� digital� logic� functions,�

�the� device� is� simply� re-programmed� using� the� ispDOWNLOAD� Cable.�

�Design� Simulation� Capability�

�Support� for� functional� simulation� of� the� control� sequence� is� provided� using� the� software� tools� Waveform� Editor� and�

�Waveform� Viewer.� Both� applications� are� spawned� from� the� LogiBuilder� environment� of� PAC-Designer.� The� simula-�

�tion� engine� combines� the� design� ?le� with� a� stimulus� ?le� (edited� by� the� user� with� Waveform� Editor)� to� produce� an�

�output� ?le� that� can� be� observed� with� the� Waveform� Viewer� (Figure� 1-19).�

�1-29�

�相关PDF资料 |

PDF描述 |

|---|---|

| ES1000-NO.4-B7-X-75MM | HEAT SHRINK TUBING |

| EBM36DCTS | CONN EDGECARD 72POS DIP .156 SLD |

| FSLBOT | KIT TOWER MECH BOARD |

| SN65LVDS31-33EVM | EVAL MOD FOR SN65LVDS31/33 |

| 4426R-3 | INDUCTOR AIR CORE 8.0NH SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISPPAC-POWR1208-01TN44I7R | 制造商:Lattice Semiconductor Corporation 功能描述: |

| ISPPAC-POWR1208P1 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:In-System Programmable Power Supply Sequencing Controller and Precision Monitor |

| ISPPACPOWR1208P101T44I | 制造商:Lattice Semiconductor Corporation 功能描述: |

| ISPPAC-POWR1208P1-01T44I | 功能描述:监控电路 PROGRAMMABLE PWR SUPPLY CONTR RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

| ISPPAC-POWR1208P1-01TN44I | 功能描述:监控电路 PROGRAMMABLE PWR SUPPLY CONTR RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。