- 您现在的位置:买卖IC网 > PDF目录16833 > KSZ8842-PMQL-EVAL (Micrel Inc)BOARD EVALUATION KSZ8842-PMQL PDF资料下载

参数资料

| 型号: | KSZ8842-PMQL-EVAL |

| 厂商: | Micrel Inc |

| 文件页数: | 46/119页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION KSZ8842-PMQL |

| 标准包装: | 1 |

| 主要目的: | 接口,以太网控制器(PHY 和 MAC) |

| 嵌入式: | 否 |

| 已用 IC / 零件: | KSZ8842-PMQL |

| 主要属性: | 2 个端口,100BASE-TX/10BASE-T |

| 次要属性: | 8/16 位接口,LinkMD 线缆诊断 |

| 已供物品: | 板 |

| 产品目录页面: | 1114 (CN2011-ZH PDF) |

| 相关产品: | 576-3348-ND - IC ETHERNET SW 2PORT 100-LFBGA 576-3089-ND - IC ETHERNT SW 2PORT PCI 100LFBGA 576-2121-ND - IC ETHERNET SW 2PORT PCI 128PQFP 576-1513-5-ND - IC SWITCH 10/100 32BIT 128-PQFP |

| 其它名称: | 576-1636 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页

Micrel, Inc.

KSZ8842-PMQL/PMBL

October 2007

32

M9999-100207-1.5

received at the high-priority receiving port are marked as high priority and are sent to the high-priority transmit queue if

the corresponding transmit queue is split. Bit 4 and 3 of registers P1CR1, P2CR1, and P3CR1 is used to enable port-

based priority for ports 1, 2, and the host port, respectively.

802.1p-Based Priority

For 802.1p-based priority, the KSZ8842-PMQL/PMBL examines the ingress (incoming) packets to determine whether

they are tagged. If tagged, the 3-bit priority field in the VLAN tag is retrieved and compared against the “priority

mapping” value, as specified by the register SGCR6. The “priority mapping” value is programmable.

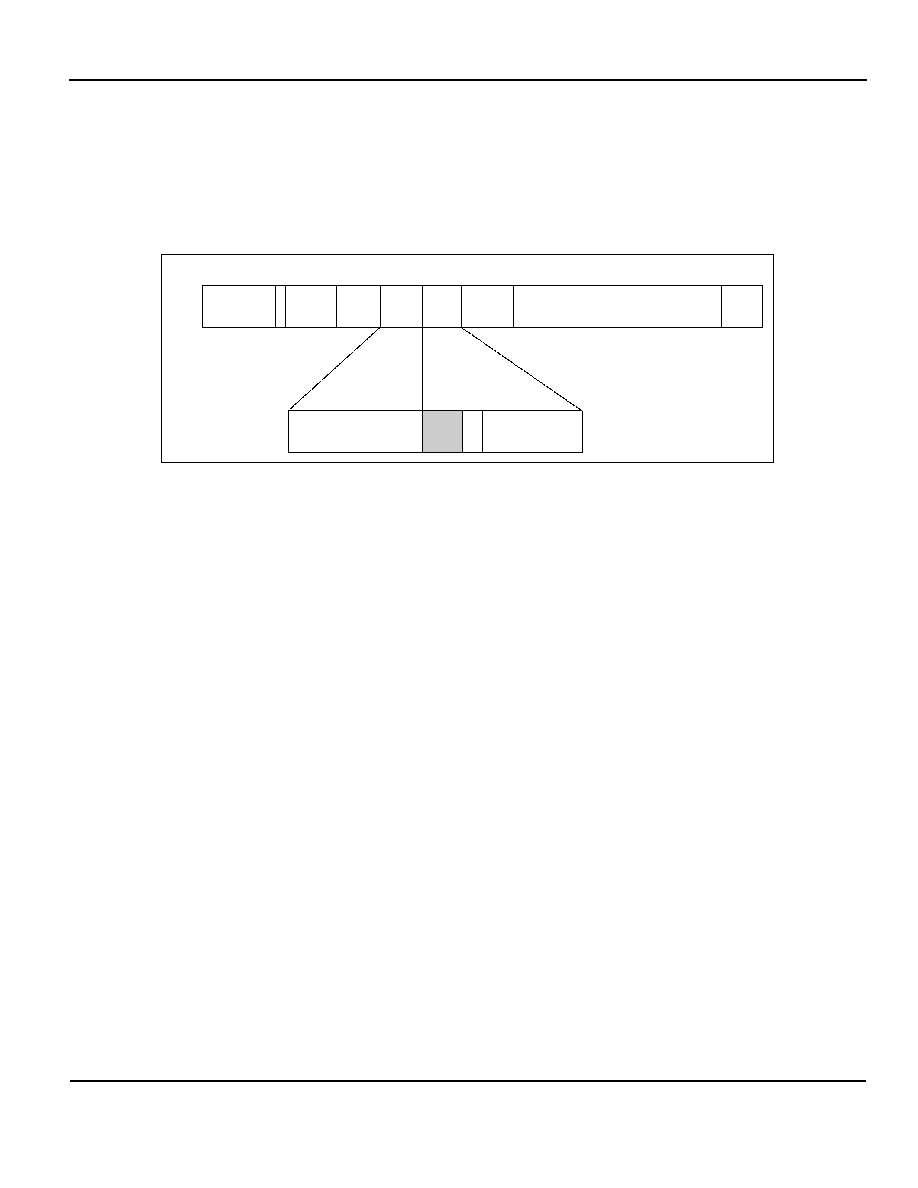

Figure 9 illustrates how the 802.1p priority field is embedded in the 802.1Q VLAN tag.

Preamble

DA

TCI

76

6

2

length

Data

FCS

2

46-1500

4

S

F

D

1

Tagged Packet Type

(8100 for Ethernet)

802.1p

CFI

VLAN ID

Bytes

Bits

16

3

12

802.1q VLAN Tag

2

SA

VPID

1

Figure 9. 802.1p Priority Field Format

802.1p based priority is enabled by bit 5 of registers P1CR1, P2CR1, and P3CR1 for ports 1, 2, and the host port,

respectively.

The KSZ8842-PMQL/PMBL provides the option to insert or remove the priority tagged frame's header at each individual

egress port. This header, consisting of the 2 bytes VLAN protocol ID (VPID) and the 2 bytes tag control information field

(TCI), is also referred to as the 802.1Q VLAN tag.

Tag insertion is enabled by bit 2 of registers P1CR1, P2CR1, and P3CR1 for ports 1, 2, and the host port, respectively.

At the egress port, untagged packets are tagged with the ingress port’s default tag. The default tags are programmed in

register sets P1VIDCR, P2VIDCR, AND P3VIDCR for ports 1, 2 and the host port, respectively. The KSZ8842-

PMQL/PMBL does not add tags to already tagged packets.

Tag removal is enabled by bit 1 of registers P1CR1, P2CR1, and P3CR1 for ports 1, 2, and the host port, respectively.

At the egress port, tagged packets will have their 802.1Q VLAN Tags removed. The KSZ8842-PMQL/PMBL will not

modify untagged packets.

The CRC is recalculated for both tag insertion and tag removal.

802.1p priority field re-mapping is a QoS feature that allows the KSZ8842-PMQL/PMBL to set the “User Priority

Ceiling” at any ingress port. If the ingress packet’s priority field has a higher priority value than the default tag’s priority

field of the ingress port, the packet’s priority field is replaced with the default tag’s priority field. The “User Priority

Ceiling” is enabled by bit 3 of registers P1CR2, P2CR2, and P3CR2 for ports 1, 2, and the host port, respectively.

DiffServ based Priority

DiffServ-based priority uses the ToS registers shown in the Priority Control Registers section. The ToS priority control

registers implement a fully decoded, 128-bit Differentiated Services Code Point (DSCP) register to determine packet

priority from the 6-bit ToS field in the IP header. When the most significant 6 bits of the ToS field are fully decoded, the

resultant of the 64 possibilities is compared with the corresponding bits in the DSCP register to determine priority.

Rate Limiting Support

The KSZ8842-PMQL/PMBL supports hardware rate limiting from 64 Kbps to 88 Mbps, independently on the “receive

side” and on the “transmit side” on a per port basis. For 10Base-T, a rate setting above 10 Mbps means the rate is not

limited. On the receive side, the data receive rate for each priority at each port can be limited by setting up Ingress Rate

Control Registers. On the transmit side, the data transmit rate for each priority queue at each port can be limited by

setting up Egress Rate Control Registers. The size of each frame has options to include minimum IFG (Inter Frame

Gap) or Preamble byte, in addition to the data field (from packet DA to FCS).

相关PDF资料 |

PDF描述 |

|---|---|

| V24C8C100B | CONVERTER MOD DC/DC 8V 100W |

| 202K185-25/225-0 | BOOT MOLDED |

| HMM06DRKH | CONN EDGECARD 12POS DIP .156 SLD |

| 202D274-4-61/42-0 | BOOT MOLDED |

| SFSD-30-28-H-10.00-SR | CABLE ASSY SOCKET 60POS 28AWG |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8842-PMQLI | 功能描述:以太网 IC 2-Port Ethernet Switch/Repeater + 32-bit/33MHz PCI bus interface, Ind Temp (Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLL | 功能描述:以太网 IC Single Ethernet Port + Generic (16-bit) Bus Interface(Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLL TR | 功能描述:以太网 IC Single Ethernet Port + Generic (16-bit) Bus Interface(Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLL-EVAL | 功能描述:以太网开发工具 Single Ethernet Port + Generic (16-bit) Bus Interface(Lead Free) Eval Board RoHS:否 制造商:Micrel 产品:Evaluation Boards 类型:Ethernet Transceivers 工具用于评估:KSZ8873RLL 接口类型:RMII 工作电源电压: |

| KSZ8851-16MLL-EVAL | 制造商:Micrel Inc 功能描述:BOARD EVALUATION FOR KSZ8851-16MLL |

发布紧急采购,3分钟左右您将得到回复。