- 您现在的位置:买卖IC网 > PDF目录16833 > KSZ8842-PMQL-EVAL (Micrel Inc)BOARD EVALUATION KSZ8842-PMQL PDF资料下载

参数资料

| 型号: | KSZ8842-PMQL-EVAL |

| 厂商: | Micrel Inc |

| 文件页数: | 49/119页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION KSZ8842-PMQL |

| 标准包装: | 1 |

| 主要目的: | 接口,以太网控制器(PHY 和 MAC) |

| 嵌入式: | 否 |

| 已用 IC / 零件: | KSZ8842-PMQL |

| 主要属性: | 2 个端口,100BASE-TX/10BASE-T |

| 次要属性: | 8/16 位接口,LinkMD 线缆诊断 |

| 已供物品: | 板 |

| 产品目录页面: | 1114 (CN2011-ZH PDF) |

| 相关产品: | 576-3348-ND - IC ETHERNET SW 2PORT 100-LFBGA 576-3089-ND - IC ETHERNT SW 2PORT PCI 100LFBGA 576-2121-ND - IC ETHERNET SW 2PORT PCI 128PQFP 576-1513-5-ND - IC SWITCH 10/100 32BIT 128-PQFP |

| 其它名称: | 576-1636 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页

Micrel, Inc.

KSZ8842-PMQL/PMBL

October 2007

35

M9999-100207-1.5

Host Communication

The descriptor lists and data buffers, collectively called the host communication, manage the actions and status related

to RX and TX buffer management. Commands and signals that control the functional operation of the KSZ8842-

PMQL/PMBL are also described.

The KSZ8842-PMQL/PMBL and the driver communicate through the two data structures: Command and status

registers (CSRs), and Descriptor Lists and Data Buffers.

Note: All unused bits of the data structure in this section are reserved and should be written by the driver as zero.

Host Communication Descriptor Lists and Data Buffers

The KSZ8842-PMQL/PMBL transfers received data frames to the receive buffer in host memory and transmits data

from the transmit buffers in host memory. Descriptors that reside in the host memory act as pointers to these buffers.

There are two descriptor lists (one for receive and one for transmit) for MAC DMA. The base address of each list is

written in the TDLB register and in the RDLB register, respectively. A descriptor list is forward linked. The last descriptor

may point back to the first entry to create a ring structure. Descriptors are chained by setting the next address to the

next buffer in both the receive and transmit descriptors.

The descriptor lists reside in the host physical memory address space. Each pointer points to one buffer and the

second pointer points to the next descriptor. This enables the greatest flexibility for the host to chain any data buffers

with discontinuous memory location. This eliminates processor-intensive tasks such as memory copying from the host

to memory.

A data buffer contains either an entire frame or part of a frame, but it cannot exceed a single frame. Buffers contain only

data; and buffer status is maintained in the descriptor. Data chaining refers to frames that span multiple data buffers.

Data chaining can be enabled or disabled. Data buffers reside in host physical memory space.

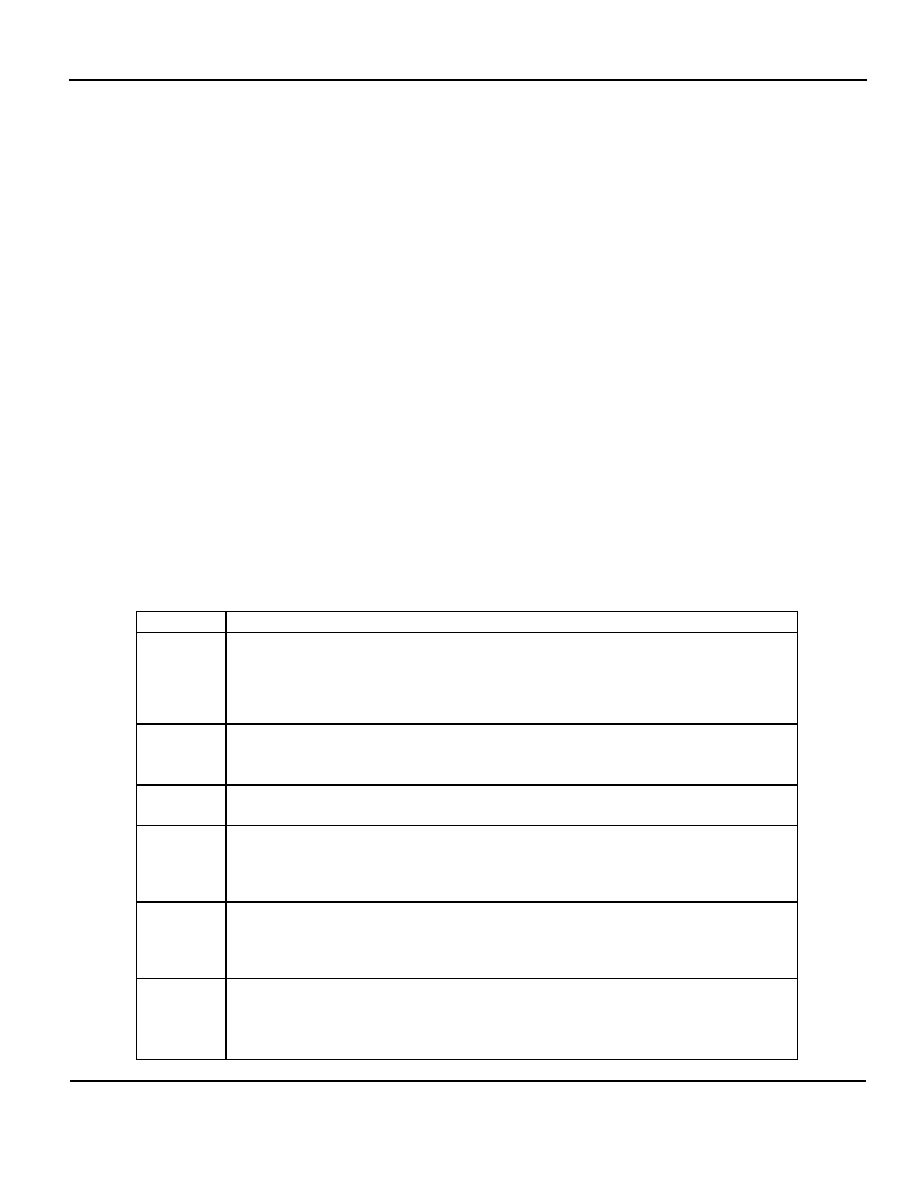

Receive Descriptors (RDES0-RDES3)

Receive descriptor and buffer addresses must be Word aligned. Each receive descriptor provides one frame buffer, one

byte count field, and control and status bits.

The following table shows the RDES0 register bit fields.

Bit

Description

31

OWN Own Bit

When set, indicates that the descriptor is owned by the KSZ8842-PMQL/PMBL.

When reset, indicates that the descriptor is owned by the host. The KSZ8842-PMQL/PMBL

clears this bit either when it completes the frame reception or when the buffers that are

associated with this descriptor are full.

30

FS First Descriptor

When set, indicates that this descriptor contains the first buffer of a frame.

If the buffer size of the first buffer is 0, the next buffer contains the beginning of the frame.

29

LS Last Descriptor

When set, indicates that the buffer pointed by this descriptor is the last buffer of the frame.

28

IPE IP Checksum Error

When set, indicates that the received frame is an IP packet and its IP checksum field does

not match.

This bit is valid only when last descriptor is set.

27

TCPE TCP Checksum Error

When set, indicates that the received frame is a TCP/IP packet and its TCP checksum field

does not match.

This bit is valid only when last descriptor is set.

26

UDPE UDP Checksum Error

When set, indicates that the received frame is an UDP/IP packet and its UDP checksum field

does not match.

This bit is valid only when last descriptor is set.

相关PDF资料 |

PDF描述 |

|---|---|

| V24C8C100B | CONVERTER MOD DC/DC 8V 100W |

| 202K185-25/225-0 | BOOT MOLDED |

| HMM06DRKH | CONN EDGECARD 12POS DIP .156 SLD |

| 202D274-4-61/42-0 | BOOT MOLDED |

| SFSD-30-28-H-10.00-SR | CABLE ASSY SOCKET 60POS 28AWG |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8842-PMQLI | 功能描述:以太网 IC 2-Port Ethernet Switch/Repeater + 32-bit/33MHz PCI bus interface, Ind Temp (Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLL | 功能描述:以太网 IC Single Ethernet Port + Generic (16-bit) Bus Interface(Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLL TR | 功能描述:以太网 IC Single Ethernet Port + Generic (16-bit) Bus Interface(Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLL-EVAL | 功能描述:以太网开发工具 Single Ethernet Port + Generic (16-bit) Bus Interface(Lead Free) Eval Board RoHS:否 制造商:Micrel 产品:Evaluation Boards 类型:Ethernet Transceivers 工具用于评估:KSZ8873RLL 接口类型:RMII 工作电源电压: |

| KSZ8851-16MLL-EVAL | 制造商:Micrel Inc 功能描述:BOARD EVALUATION FOR KSZ8851-16MLL |

发布紧急采购,3分钟左右您将得到回复。