- 您现在的位置:买卖IC网 > PDF目录177663 > LC5768VG-10F484I (LATTICE SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | LC5768VG-10F484I |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 中文描述: | EE PLD, 10 ns, PBGA484 |

| 封装: | FBGA-484 |

| 文件页数: | 15/48页 |

| 文件大小: | 237K |

| 代理商: | LC5768VG-10F484I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Lattice Semiconductor

ispMACH 5000VG Family Data Sheet

22

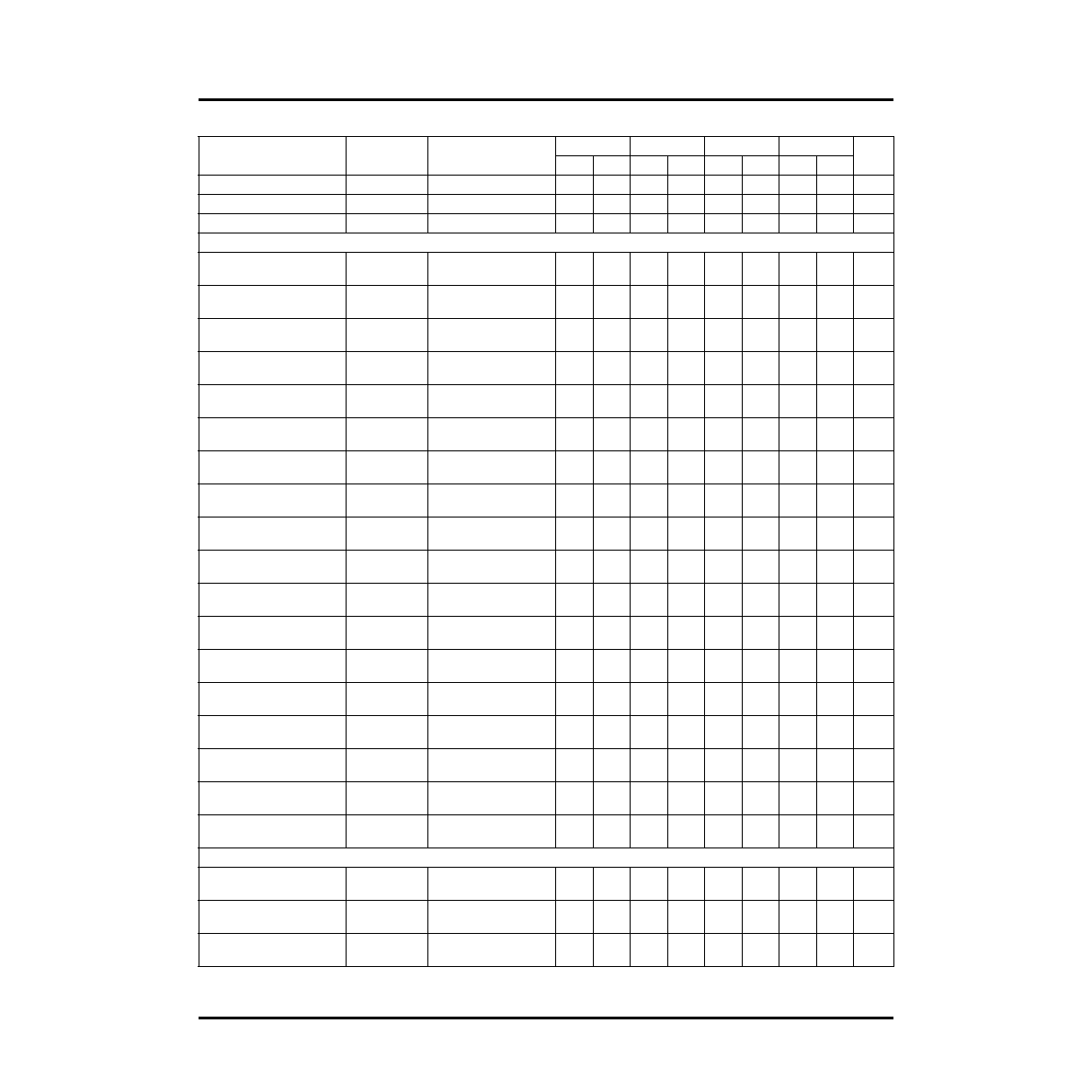

ispMACH 5768VG Timing Adders

Adder

Type

Base

Parameter

Description

-5

-75

-10

-12

Units

Min

Max

Min

Max

Min

Max

Min

Max

tBLA

tROUTE

GLB Loading Adder

—

0.0

—

0.0

—

0.0

—

0.0

ns

tEXP

tPTSA

PT Expander Adder

—

1.5

—

2.0

—

2.5

—

2.5

ns

tLP

tROUTE

Low Power Adder

—

1.5

—

1.5

—

1.5

—

1.5

ns

tIOI Input Adders

LVCMOS18_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using LVCMOS1.8

standard

—

0.90

—

0.90

—

0.90

—

0.90

ns

LVCMOS25_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using LVCMOS2.5

standard

—

0.15

—

0.15

—

0.15

—

0.15

ns

LVCMOS33_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using LVCMOS3.3

standard

—0.0—0.0—

0.0

—

0.0

ns

LVTTL

tIN, tGCLK_IN,

tRSTb, tGOE

Using LVTTL standard

—

0.0

—

0.0

—

0.0

—

0.0

ns

PCI_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using PCI standard

—

0.0

—

0.0

—

0.0

—

0.0

ns

PCI_X_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using PCI_X

standard

—0.0—0.0—

0.0

—

0.0

ns

AGP_1X_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using AGP-1X

standard

—0.0—0.0—

0.0

—

0.0

ns

SSTL3_I_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using SSTL3_I

standard

—

1.00

—

1.00

—

1.00

—

1.00

ns

SSTL3_II_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using SSTL3_II

standard

—

1.00

—

1.00

—

1.00

—

1.00

ns

SSTL2_I_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using SSTL2_I

standard

—

1.00

—

1.00

—

1.00

—

1.00

ns

SSTL2_II_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using SSTL2_II

standard

—

1.00

—

1.00

—

1.00

—

1.00

ns

CTT33_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using CTT3.3

standard

—0.0—0.0—

0.0

—

0.0

ns

CTT25_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using CTT2.5

standard

—

0.15

—

0.15

—

0.15

—

0.15

ns

HSTL_I_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using HSTL_I

standard

—

1.25

—

1.25

—

1.25

—

1.25

ns

HSTL_III_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using HSTL_III

standard

—

1.25

—

1.25

—

1.25

—

1.25

ns

GTL+_in

tIN, tGCLK_IN,

tRSTb, tGOE

Using GTL+

standard

—

1.50

—

1.50

—

1.50

—

1.50

ns

LVDS_in

tGCLK_IN

Using LVDS

standard

—

1.70

—

1.70

—

1.70

—

1.70

ns

LVPECL_in

tGCLK_IN

Using LVPECL

standard

—

2.10

—

2.10

—

2.10

—

2.10

ns

tIOO Output Adders

LVCMOS18_4mA_out

tBUF, tEN, tDIS

Output congured as

1.8V & 4mA Buffer

—

3.00

—

3.00

—

3.00

—

3.00

ns

LVCMOS18_5mA_out

tBUF, tEN, tDIS

Output congured as

1.8V & 5.33mA Buffer

—

2.50

—

2.50

—

2.50

—

2.50

ns

LVCMOS18_8mA_out

tBUF, tEN, tDIS

Output congured as

1.8V & 8mA Buffer

—

1.85

—

1.85

—

1.85

—

1.85

ns

Note: Open drain timing is the same as corresponding LVCMOS timing.

Timing v.1.20

相关PDF资料 |

PDF描述 |

|---|---|

| LC51024VG-10F484C | |

| LC5768VG-12F484I | |

| LC5768VG-12F256I | |

| LC5512B-75F256C | |

| LC5256B-75T128I | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC5768VG-12F256I | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5768VG-12F484I | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5768VG-5F256C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5768VG-5F484C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5768VG-5FN484C | 制造商:Lattice Semiconductor Corporation 功能描述:CPLD ispMACH 5000VG Family 768 Macro Cells 178.6MHz 3.3V 484-Pin FBGA |

发布紧急采购,3分钟左右您将得到回复。