- 您现在的位置:买卖IC网 > PDF目录177663 > LC5768VG-10F484I (LATTICE SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | LC5768VG-10F484I |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 中文描述: | EE PLD, 10 ns, PBGA484 |

| 封装: | FBGA-484 |

| 文件页数: | 23/48页 |

| 文件大小: | 237K |

| 代理商: | LC5768VG-10F484I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Lattice Semiconductor

ispMACH 5000VG Family Data Sheet

3

The ispMACH5000VG devices also contain sysCLOCK Phase Locked Loops (PLLs) that provide designers with

increased clocking exibility. The PLLs can be used to synthesize new clocks for use on-chip or elsewhere within

the system. They can also be used to deskew clocks, again both at the chip and system levels. A variable delay line

capability further improves this and allows designers to retard or advance the clock in order to tune set-up and

clock-to-out times for optimal results. The ispMACH 5000VG Family Selection Guide (Table 1) details the key

attributes and packages for the ispMACH 5000VG devices.

ispMACH 5000VG Architecture

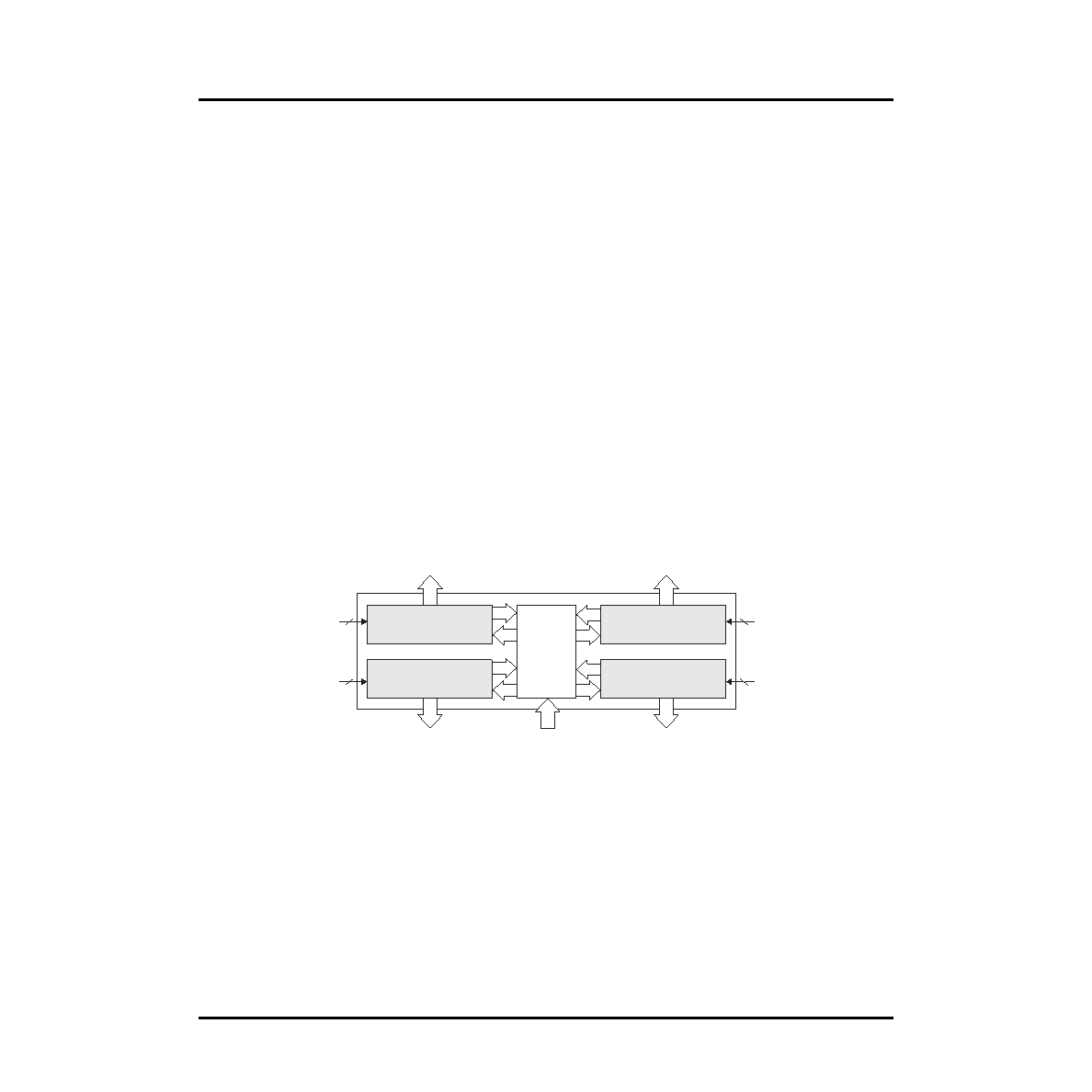

The ispMACH 5000VG Family of In-System Programmable High Density Logic Devices is based on segments con-

taining four Generic Logic Blocks (GLBs) and a hierarchical routing pool (GRP) structure interconnecting the seg-

ments. A segment routing pool (SRP) connects each GLB in a segment allowing the maximum exibility and

speed.

Outputs from the GLBs drive the Segment Routing Pool (SRP) and the Global Routing Pool (GRP). Enhanced

switching resources are provided to allow signals in the Segment Routing Pool to drive any or all the GLBs in the

segment. Optimal switching is provided to allow all signals in the Global Routing Pool to be routed to any or all

SRPs. This mechanism allows fast, efcient connections across the entire device.

Segment

Each segment contains four GLBs and a segment routing pool (SRP). Each GLB has 32 internal feedback outputs

and 16 external feedback outputs, for a total of 48 outputs from each GLB feeding the SRP. The SRP contains up to

384 signals, 48 from each GLB and 192 from the GRP, with full routing capability. This routing scheme maximizes

the exibility and speed of the device without sacricing the routing.

Generic Logic Block

Each GLB contains 32 macrocells and a fully populated, programmable AND-array with 160 logic product terms

and three control product terms. The GLB has 68 inputs from the Segment Routing Pool, which are available in

both true and complement form for every product term. The three control product terms are used for shared reset,

clock and output enable functions. Figure 3 shows the structure of the GLB from the macrocell perspective. This is

referred to as a macrocell slice. There are 32 macrocell slices per GLB.

AND-Array

The programmable AND-Array consists of 68 inputs and 163 output product terms. The 68 inputs from the SRP are

used to form 136 lines in the AND-Array (true and complement of the inputs). Each line in the array can be con-

nected to any of the 163 output product terms via a wired AND. Each of the 160 logic product terms feed the Dual-

OR Array with the remaining three control product terms feeding the Shared PT Clock, Shared PT Reset and

Shared PT OE. Every set of ve product terms from the 160 logic product terms forms a product term cluster start-

Figure 2. Segment

Clocks

4

GLB

Segment

Routing

Pool

(SRP)

48

68

48

68

48

68

48

192

From

GRP

To

GRP

To

GRP

To

GRP

Clocks

4

To

GRP

48

Clocks

4

Clocks

4

GLB

相关PDF资料 |

PDF描述 |

|---|---|

| LC51024VG-10F484C | |

| LC5768VG-12F484I | |

| LC5768VG-12F256I | |

| LC5512B-75F256C | |

| LC5256B-75T128I | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC5768VG-12F256I | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5768VG-12F484I | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5768VG-5F256C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5768VG-5F484C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5768VG-5FN484C | 制造商:Lattice Semiconductor Corporation 功能描述:CPLD ispMACH 5000VG Family 768 Macro Cells 178.6MHz 3.3V 484-Pin FBGA |

发布紧急采购,3分钟左右您将得到回复。