- 您现在的位置:买卖IC网 > PDF目录98023 > ML60851DTB (LAPIS SEMICONDUCTOR CO LTD) UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | ML60851DTB |

| 厂商: | LAPIS SEMICONDUCTOR CO LTD |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| 封装: | 10 X 10 MM, 0.80 MM PITCH, PLASTIC, TQFP-44 |

| 文件页数: | 76/84页 |

| 文件大小: | 394K |

| 代理商: | ML60851DTB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页当前第76页第77页第78页第79页第80页第81页第82页第83页第84页

FEDL60851D-01

1Semiconductor

ML60851D

77/83

Operation of 2-layer structure FIFO during bulk transfer

The FIFOs of EP1 have a 64 bytes x 2-layer structure. As a consequence, these FIFOs can temporarily store a

maximum of 128 bytes of bulk transfer data.

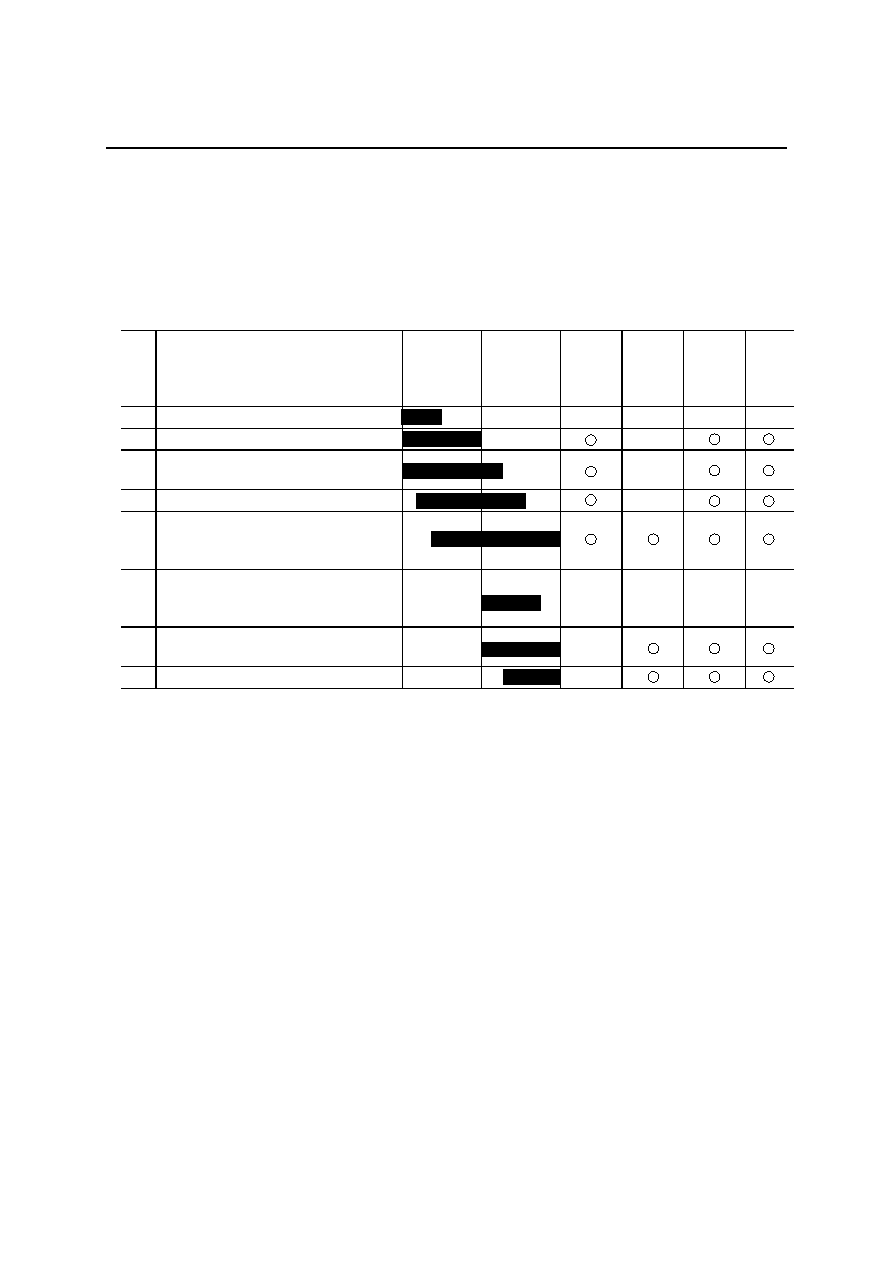

(1) 2-Layer reception operation (O indicates the assert condition and X indicates de-assert condition)

The following description assumes that interrupt has been enabled for EP1 (D1 of INTENBL=1)

In the case of 1

→2→3→4→5a→6

In the case of 1

→2→3→4→5b→6

Layer A

64 bytes

Layer B

64 bytes

Layer A

PKT

RDY

Layer B

PKT

RDY

EP1

receive

PKT

RDY

INTR

1

Start storing data in layer A of reception

××

×

2

Data of one packet has been stored.

×

3

Start reception and storing of data in

layer B.

×

4

Local MCU starts reading layer A.

×

5a

When the storing of packet in layer B is

completed following the completion of

reading layer A.

5b

When the reading of packet in layer A

is completed following the completion

of storing data in layer B.

××

×

6

From 5a: Layer A has become empty.

From 5b: Layer B has become full.

×

7

Start reading layer B.

×

When one packet of receive data is stored in layer A of the FIFO and EOP is received, the ML60851D asserts

the packet ready bit of EP1 and also asserts the

INTR pin. This makes it possible for the local MCU to read the

receive data.

Subsequently, data can be received from the host, and the ML60851D switches the FIFO for storing to layer B.

When one packet of data described above has been read from layer A of the FIFO, make the local MCU reset

the receive packet ready status of EP1 (by writing a “1” into bit D1 of PKTRDY).

At the time the EP1 receive packet ready status is reset, if the reception of layer B has not been completed, the

ML60851D resets the EP1 receive packet ready status and de-asserts the

INTR pin.

However, if the reception of layer B has been completed at the time the EP1 receive packet ready status is reset,

the ML60851D rejects the request from the local MCU to reset the EP1 receive packet ready status, and

continues to maintain the EP1 receive packet ready status and the asserted condition of the

INTR pin.

相关PDF资料 |

PDF描述 |

|---|---|

| ML60852A | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| ML63187-XXXGA | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, PQFP128 |

| ML63193-XXXWA | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, UUC128 |

| ML64168-XXX | 4-BIT, MROM, 0.7 MHz, MICROCONTROLLER, UUC80 |

| ML64P168-NGP | 4-BIT, OTPROM, 0.7 MHz, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ML60851E | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60851EGA | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60851ETB | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60852 | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60852A | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

发布紧急采购,3分钟左右您将得到回复。