- 您现在的位置:买卖IC网 > PDF目录45376 > MPM22CGA800A (INTEL CORP) 32-BIT, 800 MHz, MICROPROCESSOR, XMA PDF资料下载

参数资料

| 型号: | MPM22CGA800A |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 800 MHz, MICROPROCESSOR, XMA |

| 封装: | MMC-2 |

| 文件页数: | 13/68页 |

| 文件大小: | 966K |

| 代理商: | MPM22CGA800A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

Pentium

III Processor Mobile Module MMC-2

Featuring Intel

SpeedStep Technology

14

Datasheet

243356-006

3.1.8

Clock Signals

Table 8 provides descriptions of the clock signals.

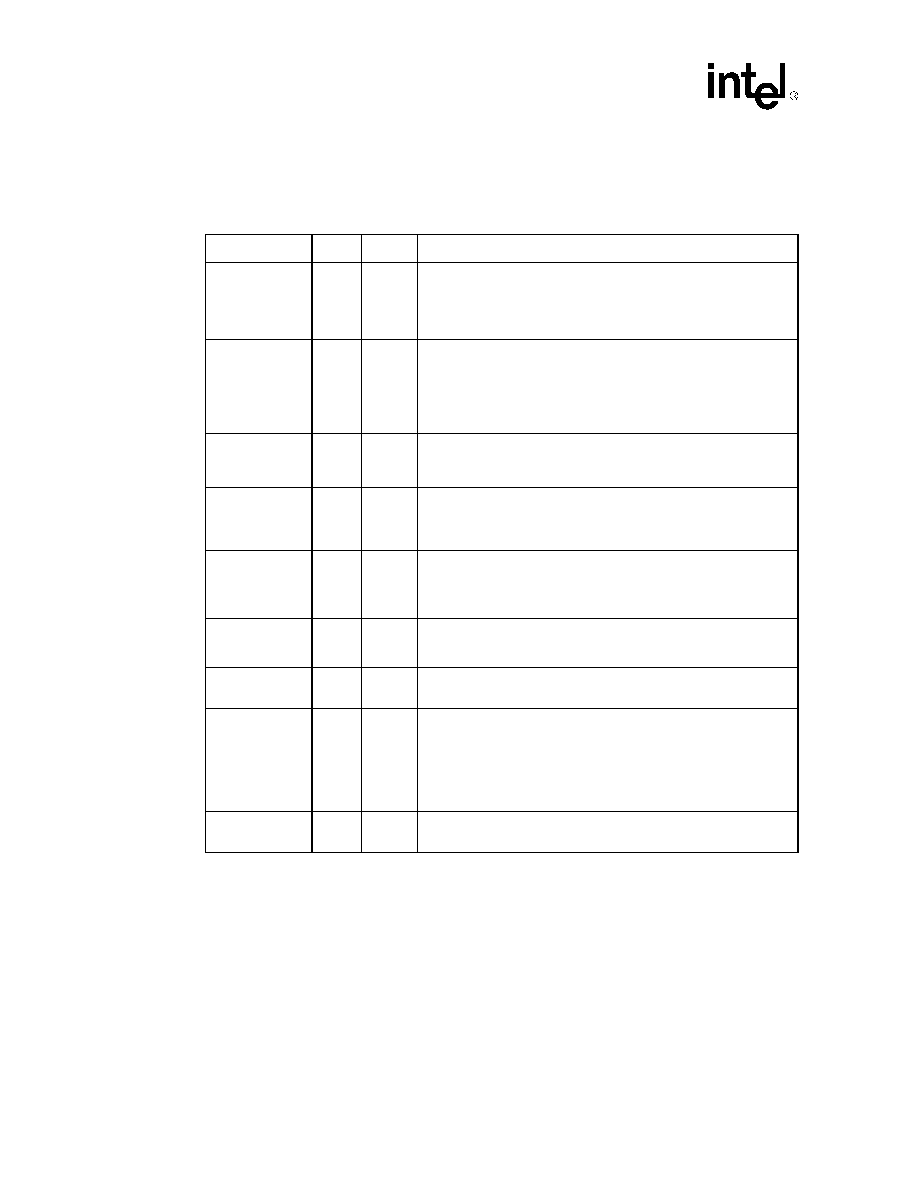

Table 8.

Clock Signal Descriptions

Name

Type

Voltage

Description

PCLK

I

PCI

V_3

PCI Clock In: PCLK, an input to the mobile module, is one of the

system’s PCI clocks. This clock is used by all of the 82443BX Host

Bridge logic in the PCI clock domain. This clock is stopped when the

PIIX4E/M PCI_STP# signal is asserted "and/or" during all suspend

states.

HCLK0

I

CMOS

V_CLK

Host Clock In: This clock is an input to the mobile module from the

CK100-M/CK100-SM clock source. The processor and the 82443BX

Host Bridge system controller use HCLK0. This clock is stopped when

the PIIX4E/M CPU_STP# signal is asserted "and/or" during all

suspend states.

Note: The signal names HCLK0 and BCLK are used interchangeably.

HCLK1

I

CMOS

V_CLK

Host Clock In: This clock is an input to the mobile module from the

CK100-M/CK100-SM clock source.

HCLK1 is not implemented on the mobile module.

DCLK0

O

CMOS

V_3

SDRAM Clock Out: A 66-MHz SDRAM clock reference generated

internally by the 82443BX Host Bridge system controller onboard PLL.

It feeds an external buffer that produces multiple copies for the SO-

DIMMs.

DCLKRD

I

CMOS

V_3

SDRAM Read Clock: A feedback reference from the SDRAM clock

buffer. The 82443BX Host Bridge System Controller uses this clock

when reading data from the SDRAM array.

DCLKRD is not implemented on the mobile module.

DCLKWR

I

CMOS

V_3

SDRAM Write Clock: A feedback reference from the SDRAM clock

buffer. The 82443BX Host Bridge system controller uses this clock

when writing data to the SDRAM array.

GCLKIN

I

CMOS

V_3

AGP Clock In: The GCLKIN input is a feedback reference from the

GCLKO signal.

GCLKO

O

CMOS

V_3

AGP Clock Out: This signal is generated by the 82443BX Host

Bridge system controller onboard PLL from the HCLK0 host clock

reference. The frequency of GCLKO is 66 MHz. The GCLKO output is

used to feed both the PLL reference input pins on the 82443BX Host

Bridge system controller and the AGP device. The board layout must

maintain complete symmetry on loading and trace geometry to

minimize AGP clock skew.

FQS

O

CMOS

V_3S

Frequency Select: This output indicates the desired host clock

frequency for the mobile module.

相关PDF资料 |

PDF描述 |

|---|---|

| MPM22PDA266B | 32-BIT, 266 MHz, MICROPROCESSOR, XMA |

| MPM22PDA366B | 32-BIT, 366 MHz, MICROPROCESSOR, XMA |

| MPM22PDA266A | 32-BIT, 266 MHz, MICROPROCESSOR, XMA |

| MPM22PDA300A | 32-BIT, 300 MHz, MICROPROCESSOR, XMA |

| MPM22PDA300B | 32-BIT, 300 MHz, MICROPROCESSOR, XMA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPM-25S | 制造商:MPD 制造商全称:MicroPower Direct, LLC 功能描述:Universal Input, 25W Miniature, PC Mount AC/DC Power Supplies |

| MPM-25S-05 | 制造商:MPD 制造商全称:MicroPower Direct, LLC 功能描述:Universal Input, 25W Miniature, PC Mount AC/DC Power Supplies |

| MPM-25S-12 | 制造商:MPD 制造商全称:MicroPower Direct, LLC 功能描述:Universal Input, 25W Miniature, PC Mount AC/DC Power Supplies |

| MPM-25S-15 | 制造商:MPD 制造商全称:MicroPower Direct, LLC 功能描述:Universal Input, 25W Miniature, PC Mount AC/DC Power Supplies |

| MPM-25S-24 | 制造商:MPD 制造商全称:MicroPower Direct, LLC 功能描述:Universal Input, 25W Miniature, PC Mount AC/DC Power Supplies |

发布紧急采购,3分钟左右您将得到回复。