- 您现在的位置:买卖IC网 > PDF目录385639 > MT49H8M32FM (Micron Technology, Inc.) REDUCED LATENCY DRAM RLDRAM PDF资料下载

参数资料

| 型号: | MT49H8M32FM |

| 厂商: | Micron Technology, Inc. |

| 英文描述: | REDUCED LATENCY DRAM RLDRAM |

| 中文描述: | 低延迟DRAM延迟DRAM |

| 文件页数: | 11/43页 |

| 文件大小: | 652K |

| 代理商: | MT49H8M32FM |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页

11

256: x16, x32 RLDRAM

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V V

EXT

, 1.8V V

DD

, 1.8V V

DD

Q, RLDRAM

IEEE 1149.1 SERIAL BOUNDARY SCAN

(JTAG)

The RLDRAM incorporates a serial boundary scan

Test Access Port (TAP). This port operates in accordance

with IEEE Standard 1149.1-1990 but does not have the

set of functions required for full 1149.1 compliance. These

functions from the IEEE specification are excluded be-

cause their inclusion places an added delay in the critical

speed path of the RLDRAM. Note that the TAP controller

functions in a manner that does not conflict with the

operation of other devices using 1149.1 fully compliant

TAPs. The TAP operates using JEDEC-standard 1.8V I/O

logic levels.

The RLDRAM contains a TAP controller, instruction

register, boundary scan register, bypass register, and ID

register.

DISABLING THE JTAG FEATURE

It is possible to operate the RLDRAM without using the

JTAG feature. To disable the TAP controller, TCK must be

tied LOW (V

SS

) to prevent clocking of the device. TDI and

TMS are internally pulled up and may be unconnected.

They may alternately be connected to V

DD

through a pull-

up resistor. TDO should be left unconnected. Upon power-

up, the device will come up in a reset state which will not

interfere with the operation of the device.

TEST ACCESS PORT (TAP)

TEST CLOCK (TCK)

The test clock is used only with the TAP controller. All

inputs are captured on the rising edge of TCK. All outputs

are driven from the falling edge of TCK.

TEST MODE SELECT (TMS)

The TMS input is used to give commands to the TAP

controller and is sampled on the rising edge of TCK. It is

allowable to leave this pin unconnected if the TAP is not

used. The pin is pulled up internally, resulting in a logic

HIGH level.

TEST DATA-IN (TDI)

The TDI pin is used to serially input information into the

registers and can be connected to the input of any of the

registers. The register between TDI and TDO is chosen by

the instruction that is loaded into the TAP instruction

register. For information on loading the instruction regis-

ter, see Figure 1. TDI is internally pulled up and can be

unconnected if the TAP is unused in an application. TDI

is connected to the most significant bit (MSB) of any

register. (See Figure 2.)

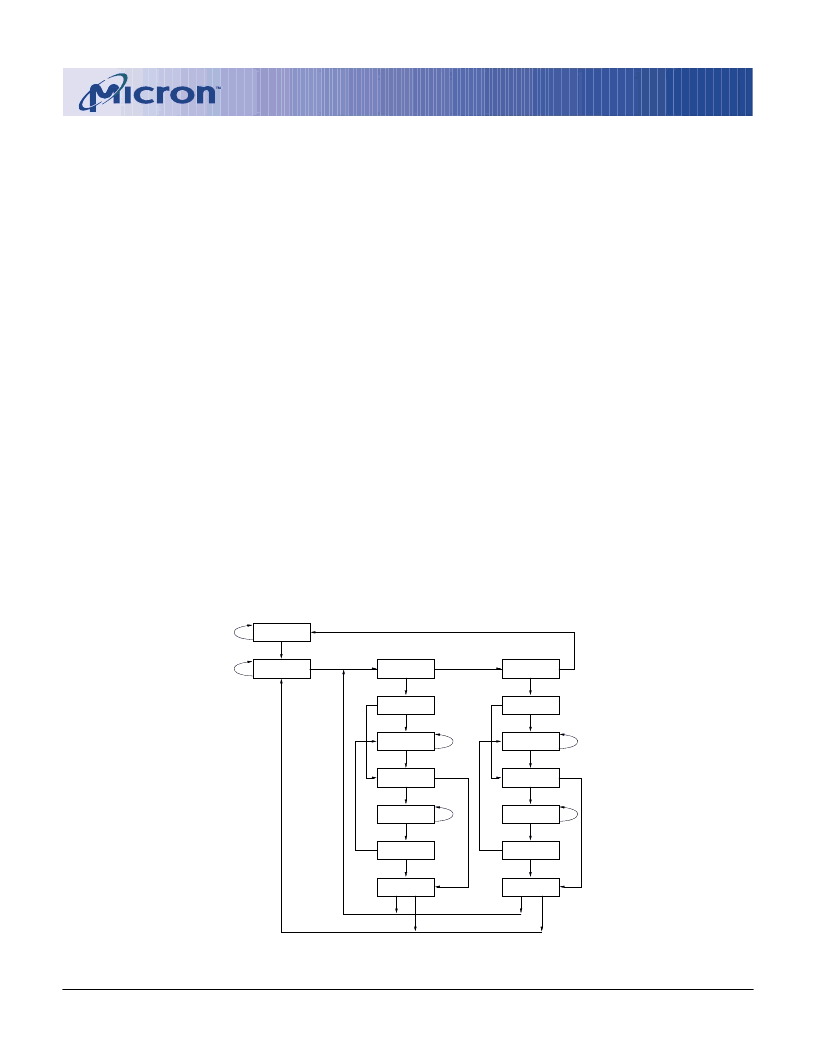

Figure 1

TAP Controller State Diagram

NOTE:

The 0/1 next to each state represents the value of TMS at the rising edge of TCK.

TEST-LOGIC

RESET

RUN-TEST/

IDLE

SELECT

DR-SCAN

SELECT

IR-SCAN

CAPTURE-DR

SHIFT-DR

CAPTURE-IR

SHIFT-IR

EXIT1-DR

PAUSE-DR

EXIT1-IR

PAUSE-IR

EXIT2-DR

UPDATE-DR

EXIT2-IR

UPDATE-IR

1

1

1

0

1

1

0

0

1

1

1

0

0

0

0

0

0

0

0

0

1

0

1

1

0

1

0

1

1

1

1

0

相关PDF资料 |

PDF描述 |

|---|---|

| MT4C1M16E5DJ-6 | EDO DRAM |

| MT4LC1M16E5DJ-6S | EDO DRAM |

| MT4LC1M16E5 | EDO DRAM |

| MT4C4256 | 256K x 4 DRAM Standard Or Low Power, Extended Refresh(标准或低功率,扩展刷新,256K x 4动态RAM) |

| MT4C4256L | 256K x 4 DRAM Standard Or Low Power, Extended Refresh(标准或低功率,扩展刷新,256K x 4动态RAM) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT49H8M32FM-33 ES | 制造商:Micron Technology Inc 功能描述:DRAM CHIP RLDRAM 256MBIT 1.8V 144PIN UBGA - Trays |

| MT49H8M32FM-33 TR | 制造商:Micron Technology Inc 功能描述:8MX32 RLDRAM PLASTIC FBGA 1.8V COMMON I/O 8 BANKS 1.8V I/O - Tape and Reel |

| MT49H8M32FM-4 | 制造商:Micron Technology Inc 功能描述:DRAM CHIP RLDRAM 256MBIT 1.8V 144PIN UBGA - Trays |

| MT49H8M32FM-4 ES | 制造商:Micron Technology Inc 功能描述:DRAM CHIP RLDRAM 256MBIT 1.8V 144PIN UBGA - Trays |

| MT49H8M32FM-5 ES | 制造商:Micron Technology Inc 功能描述:DRAM CHIP RLDRAM 256MBIT 1.8V 144FBGA - Trays |

发布紧急采购,3分钟左右您将得到回复。