- 您现在的位置:买卖IC网 > PDF目录299522 > MT58L128V18PF-6 (CYPRESS SEMICONDUCTOR CORP) 128K X 18 STANDARD SRAM, 3.5 ns, PBGA165 PDF资料下载

参数资料

| 型号: | MT58L128V18PF-6 |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | SRAM |

| 英文描述: | 128K X 18 STANDARD SRAM, 3.5 ns, PBGA165 |

| 封装: | FBGA-165 |

| 文件页数: | 14/25页 |

| 文件大小: | 647K |

| 代理商: | MT58L128V18PF-6 |

21

2Mb: 128K x 18, 64K x 32/36 Pipelined, SCD SyncBurst SRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT58L128L18P_2.p65 – Rev. 8/00

2000, Micron Technology, Inc.

2Mb: 128K x 18, 64K x 32/36

PIPELINED, SCD SYNCBURST SRAM

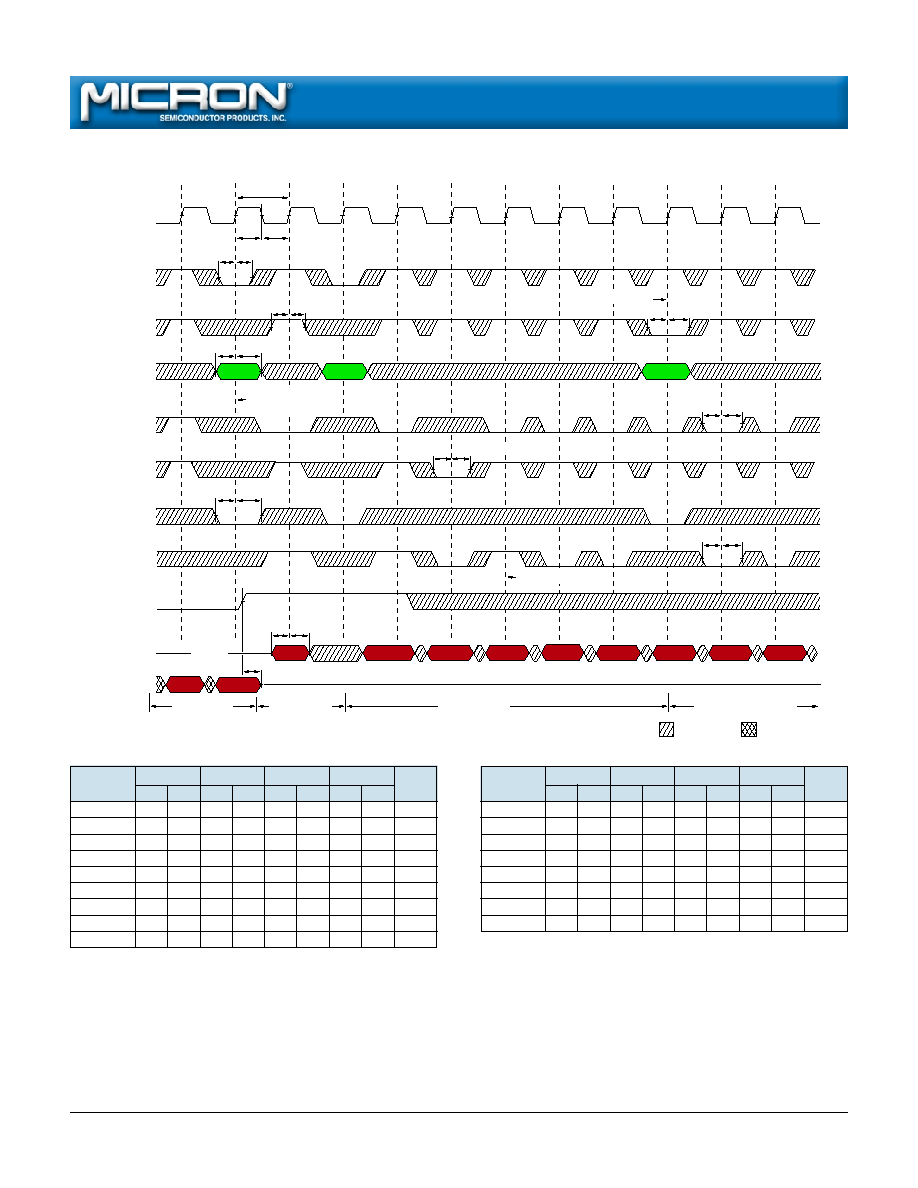

WRITE TIMING

tKC

tKL

CLK

ADSP#

tADSH

tADSS

ADDRESS

tKH

OE#

ADSC#

CE#

(NOTE 2)

tAH

tAS

A1

tCEH

tCES

BWE#,

BWa#-BWd#

Q

High-Z

ADV#

BURST READ

BURST WRITE

D(A2)

D(A2 + 1)

D(A1)

D(A3)

D(A3 + 1)

D(A3 + 2)

D(A2 + 3)

A2

A3

D

Extended BURST WRITE

D(A2 + 2)

Single WRITE

tADSH

tADSS

tADSH

tADSS

tOEHZ

tAAH

tAAS

tWH

tWS

tDH

tDS

(NOTE 3)

(NOTE 1)

(NOTE 4)

GW#

tWH

tWS

(NOTE 5)

Byte write signals are

ignored for first cycle when

ADSP# initiates burst.

ADSC# extends burst.

ADV# suspends burst.

DON’T CARE

UNDEFINED

NOTE: 1. D(A2) refers to input for address A2. Q(A2 + 1) refers to input for the next internal burst address following A2.

2. CE2# and CE2 have timing identical to CE#. On this diagram, when CE# is LOW, CE2# is LOW and CE2 is HIGH.

When CE# is HIGH, CE2# is HIGH and CE2 is LOW.

3. OE# must be HIGH before the input data setup and held HIGH throughout the data hold time. This prevents

input/output data contention for the time period prior to the byte write enable inputs being sampled.

4. ADV# must be HIGH to permit a WRITE to the loaded address.

5. Full-width WRITE can be initiated by GW# LOW; or GW# HIGH and BWE#, BWa# and BWb# LOW for x18 device;

or GW# HIGH and BWE#, BWa#-BWd# LOW for x32 and x36 devices.

-5

-6

-7.5

-10

SYMBOL

MIN MAX MIN MAX MIN MAX MIN MAX UNITS

tDS

1.5

2.2

ns

tCES

1.5

2.2

ns

tAH

0.5

ns

tADSH

0.5

ns

tAAH

0.5

ns

tWH

0.5

ns

tDH

0.5

ns

tCEH

0.5

ns

WRITE TIMING PARAMETERS

-5

-6

-7.5

-10

SYMBOL

MIN MAX MIN MAX MIN MAX MIN MAX UNITS

tKC

5.0

6.0

7.5

10

ns

fKF

200

166

133

100

MHz

tKH

1.6

1.7

1.9

3.2

ns

tKL

1.6

1.7

1.9

3.2

ns

tOEHZ

3.0

3.5

4.0

4.5

ns

tAS

1.5

2.2

ns

tADSS

1.5

2.2

ns

tAAS

1.5

2.2

ns

tWS

1.5

2.2

ns

相关PDF资料 |

PDF描述 |

|---|---|

| MT58L64V36PF-10 | 64K X 36 STANDARD SRAM, 5 ns, PBGA165 |

| MT58L256L36FS-8.8 | 256K X 36 STANDARD SRAM, 7.5 ns, PQFP100 |

| MT58LC64K16E1S27BDC1 | 64K X 16 STANDARD SRAM, UUC75 |

| MT58LC64K16E1S27BDC3-8.5 | 64K X 16 STANDARD SRAM, 8.5 ns, UUC75 |

| MT58LC64K32C4LG-5L | 64K X 32 STANDARD SRAM, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT58L128V18PT-7.5 | 制造商:Micron Technology Inc 功能描述: |

| MT58L128V32F1 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:4Mb: 256K x 18, 128K x 32/36 FLOW-THROUGH SYNCBURST SRAM |

| MT58L128V32P1T-10 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

| MT58L128V32P1T-7.5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MT58L128V36F1 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:4Mb: 256K x 18, 128K x 32/36 FLOW-THROUGH SYNCBURST SRAM |

发布紧急采购,3分钟左右您将得到回复。