- 您现在的位置:买卖IC网 > PDF目录299522 > MT58L128V18PF-6 (CYPRESS SEMICONDUCTOR CORP) 128K X 18 STANDARD SRAM, 3.5 ns, PBGA165 PDF资料下载

参数资料

| 型号: | MT58L128V18PF-6 |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | SRAM |

| 英文描述: | 128K X 18 STANDARD SRAM, 3.5 ns, PBGA165 |

| 封装: | FBGA-165 |

| 文件页数: | 22/25页 |

| 文件大小: | 647K |

| 代理商: | MT58L128V18PF-6 |

6

2Mb: 128K x 18, 64K x 32/36 Pipelined, SCD SyncBurst SRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT58L128L18P_2.p65 – Rev. 8/00

2000, Micron Technology, Inc.

2Mb: 128K x 18, 64K x 32/36

PIPELINED, SCD SYNCBURST SRAM

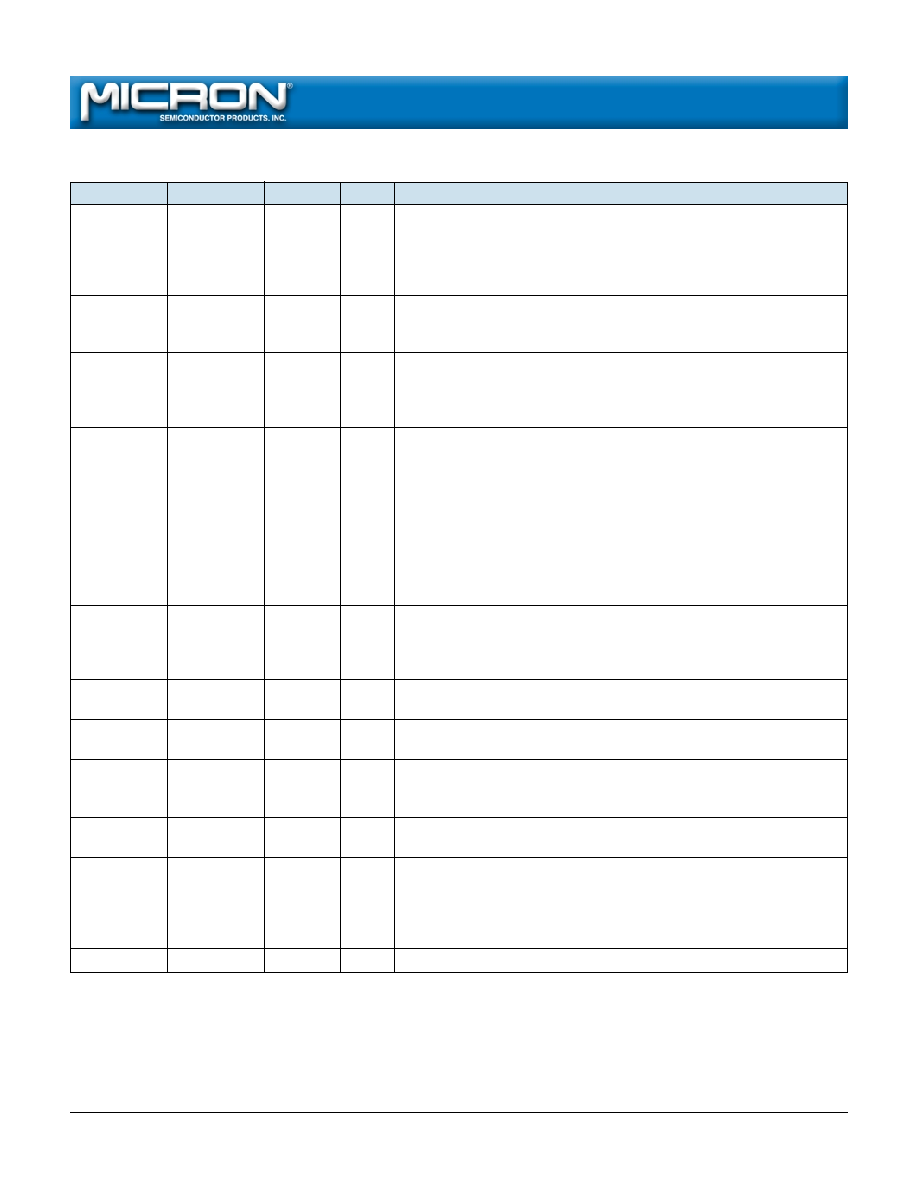

TQFP PIN DESCRIPTIONS (continued)

x18

x32/x36

SYMBOL

TYPE

DESCRIPTION

85

ADSC#

Input

Synchronous Address Status Controller: This active LOW input

interrupts any ongoing burst, causing a new external address to be

registered. A READ or WRITE is performed using the new address if

CE# is LOW. ADSC# is also used to place the chip into power-down

state when CE# is HIGH.

31

MODE

Input

Mode: This input selects the burst sequence. A LOW on this pin

selects “linear burst.” NC or HIGH on this pin selects “interleaved

burst.” Do not alter input state while device is operating.

64

ZZ

Input

Snooze Enable: This active HIGH, asynchronous input causes the

device to enter a low-power standby mode in which all data in the

memory array is retained. When ZZ is active, all other inputs are

ignored.

(a) 58, 59,

(a) 52, 53,

DQa

Input/ SRAM Data I/Os: For the x18 version, Byte “a” is associated with

62, 63, 68, 69, 56-59, 62, 63

Output DQa pins; Byte “b” is associated with DQb pins. For the x32 and x36

72, 73

versions, Byte “a” is associated with DQa pins; Byte “b” is

(b) 8, 9, 12,

(b) 68, 69,

DQb

associated with DQb pins; Byte “c” is associated with DQc pins;

13, 18, 19, 22, 72-75, 78, 79

Byte “d” is associated with DQd pins. Input data must meet setup

23

and hold times around the rising edge of CLK.

(c) 2, 3, 6-9,

DQc

12, 13

(d) 18, 19,

DQd

22-25, 28, 29

74

51

NC/DQPa

NC/

No Connect/Parity Data I/Os: On the x32 version, these pins are No

24

80

NC/DQPb

I/O

Connect (NC). On the x18 version, Byte “a” parity is DQPa; Byte “b”

–

1

NC/DQPc

parity is DQPb. On the x36 version, Byte “a” parity is DQPa; Byte

–

30

NC/DQPd

“b” parity is DQPb; Byte “c” parity is DQPc; Byte “d” parity is DQPd.

14, 15, 41, 65, 14, 15, 41, 65,

VDD

Supply Power Supply: See DC Electrical Characteristics and Operating

91

Conditions for range.

4, 11, 20, 27, 4, 11, 20, 27,

VDDQ

Supply Isolated Output Buffer Supply: See DC Electrical Characteristics and

54, 61, 70, 77 54, 61, 70, 77

Operating Conditions for range.

5, 10, 17, 21, 5, 10, 17, 21,

VSS

Supply Ground:GND.

26, 40, 55, 60, 26, 40, 55, 60,

67, 71, 76, 90 67, 71, 76, 90

38, 39, 42, 43 38, 39, 42, 43

DNU

–

Do Not Use: These signals may either be unconnected or wired to

GND to improve package heat dissipation.

1-3, 6, 7, 16,

16, 66

NC

–

No Connect: These signals are not internally connected and may be

25, 28-30,

connected to ground to improve package heat dissipation.

51-53, 56, 57,

66, 75, 78, 79,

95, 96

50

NC/SA

–

No Connect: This pin is reserved for address expansion.

相关PDF资料 |

PDF描述 |

|---|---|

| MT58L64V36PF-10 | 64K X 36 STANDARD SRAM, 5 ns, PBGA165 |

| MT58L256L36FS-8.8 | 256K X 36 STANDARD SRAM, 7.5 ns, PQFP100 |

| MT58LC64K16E1S27BDC1 | 64K X 16 STANDARD SRAM, UUC75 |

| MT58LC64K16E1S27BDC3-8.5 | 64K X 16 STANDARD SRAM, 8.5 ns, UUC75 |

| MT58LC64K32C4LG-5L | 64K X 32 STANDARD SRAM, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT58L128V18PT-7.5 | 制造商:Micron Technology Inc 功能描述: |

| MT58L128V32F1 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:4Mb: 256K x 18, 128K x 32/36 FLOW-THROUGH SYNCBURST SRAM |

| MT58L128V32P1T-10 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

| MT58L128V32P1T-7.5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MT58L128V36F1 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:4Mb: 256K x 18, 128K x 32/36 FLOW-THROUGH SYNCBURST SRAM |

发布紧急采购,3分钟左右您将得到回复。