- 您现在的位置:买卖IC网 > PDF目录224506 > MT58L128V36P1B-4 128K X 36 STANDARD SRAM, 2.3 ns, PBGA119 PDF资料下载

参数资料

| 型号: | MT58L128V36P1B-4 |

| 元件分类: | SRAM |

| 英文描述: | 128K X 36 STANDARD SRAM, 2.3 ns, PBGA119 |

| 封装: | 14 X 22 MM, PLASTIC, MS-028BHA, BGA-119 |

| 文件页数: | 35/35页 |

| 文件大小: | 353K |

| 代理商: | MT58L128V36P1B-4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页

9

4Mb: 256K x 18, 128K x 32/36 Pipelined, SCD SyncBurst SRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT58L256L18P1_D.p65 – Rev. 10/01

2001, Micron Technology, Inc.

4Mb: 256K x 18, 128K x 32/36

PIPELINED, SCD SYNCBURST SRAM

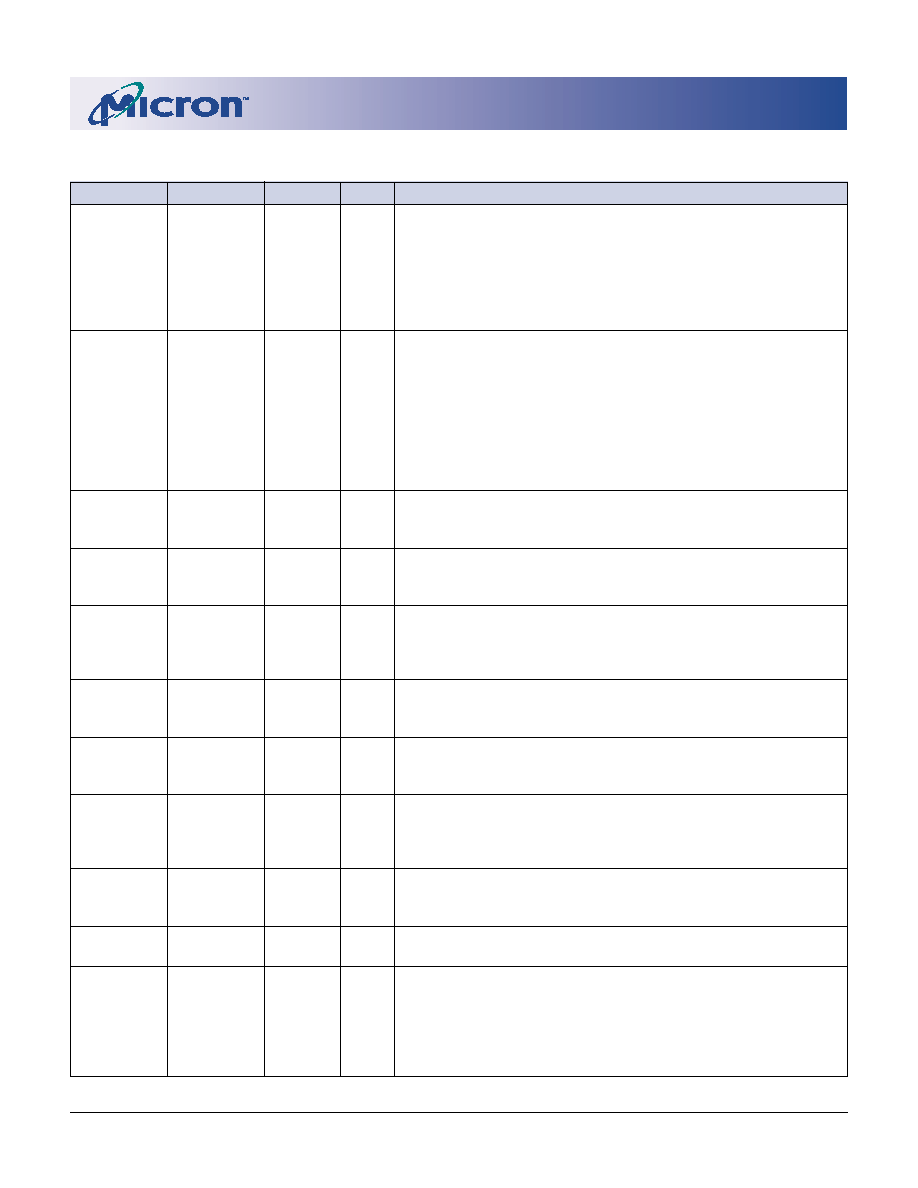

FBGA PIN DESCRIPTIONS

x18

x32/x36

SYMBOL

TYPE

DESCRIPTION

6R

SA0

Input

Synchronous Address Inputs: These inputs are registered and must

6P

SA1

meet the setup and hold times around the rising edge of CLK.

2A, 2B, 3P,

SA

3R, 4P, 4R,

8P, 8R, 9P, 9R,

8P, 8R, 9P,

10A, 10B, 10P, 9R, 10A, 10B,

10R, 11A, 11R 10P, 10R, 11R

5B

BWa#

Input

Synchronous Byte Write Enables: These active LOW inputs allow

4A

5A

BWb#

individual bytes to be written and must meet the setup and hold

–

4A

BWc#

times around the rising edge of CLK. A byte write enable is LOW

–

4B

BWd#

for a WRITE cycle and HIGH for a READ cycle. For the x18 version,

BWa# controls DQas and DQPa; BWb# controls DQbs and DQPb. For

the x32 and x36 versions, BWa# controls DQas and DQPa; BWb#

controls DQbs and DQPb; BWc# controls DQcs and DQPc; BWd#

controls DQds and DQPd. Parity is only available on the x18 and x36

versions.

7A

BWE#

Input

Byte Write Enable: This active LOW input permits BYTE WRITE

operations and must meet the setup and hold times around the

rising edge of CLK.

7B

GW#

Input

Global Write: This active LOW input allows a full 18-, 32-, or 36-bit

WRITE to occur independent of the BWE# and BWx# lines and must

meet the setup and hold times around the rising edge of CLK.

6B

CLK

Input

Clock: This signal registers the address, data, chip enable, byte write

enables, and burst control inputs on its rising edge. All synchronous

inputs must meet setup and hold times around the clock’s rising

edge.

3A

CE#

Input

Synchronous Chip Enable: This active LOW input is used to enable

the device and conditions the internal use of ADSP#. CE# is sampled

only when a new external address is loaded.

6A

CE2#

Input

Synchronous Chip Enable: This active LOW input is used to enable

the device and is sampled only when a new external address is

loaded.

11H

ZZ

Input

Snooze Enable: This active HIGH, asynchronous input causes the

device to enter a low-power standby mode in which all data in the

memory array is retained. When ZZ is active, all other inputs are

ignored.

3B

CE2

Input

Synchronous Chip Enable: This active HIGH input is used to enable

the device and is sampled only when a new external address is

loaded.

8B

OE#(G#)

Input

Output Enable: This active LOW, asynchronous input enables the

data I/O output drivers.

9A

ADV#

Input

Synchronous Address Advance: This active LOW input is used to

advance the internal burst counter, controlling burst access after the

external address is loaded. A HIGH on ADV# effectively causes wait

states to be generated (no address advance). To ensure use of

correct address during a WRITE cycle, ADV# must be HIGH at the

rising edge of the first clock after an ADSP# cycle is initiated.

(continued on next page)

相关PDF资料 |

PDF描述 |

|---|---|

| MT58L32L36PT-7.5 | 32K X 36 CACHE SRAM, 4.2 ns, PQFP100 |

| MT58L512L18DS-7.5IT | 512K X 18 CACHE SRAM, 4 ns, PQFP100 |

| MT58L512L18DT-10IT | 512K X 18 CACHE SRAM, 5 ns, PQFP100 |

| MT58L512L18PB-6IT | 512K X 18 STANDARD SRAM, 3.5 ns, PBGA119 |

| MT58L512L18PS-7.5IT | 512K X 18 CACHE SRAM, 4 ns, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT58L128V36P1F-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

| MT58L128V36P1F-6 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

| MT58L128V36P1T-7.5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

| MT58L1MV18D | 制造商:MICRON 制造商全称:Micron Technology 功能描述:8Mb: 512K x 18, 256K x 32/36 3.3V I/O, PIPELINED, DCD SYNCBURST SRAM |

| MT58L1MY18D | 制造商:MICRON 制造商全称:Micron Technology 功能描述:16Mb SYNCBURST⑩ SRAM |

发布紧急采购,3分钟左右您将得到回复。