- 您现在的位置:买卖IC网 > Datasheet目录490 > NTMD2C02R2SG (ON Semiconductor)MOSFET N/P-CH COMPL 20V 8-SOIC Datasheet资料下载

参数资料

| 型号: | NTMD2C02R2SG |

| 厂商: | ON Semiconductor |

| 文件页数: | 5/12页 |

| 文件大小: | 0K |

| 描述: | MOSFET N/P-CH COMPL 20V 8-SOIC |

| 产品变化通告: | Wire Change 20/Aug/2008 Product Discontinuation 01/Oct/2008 |

| 标准包装: | 2,500 |

| FET 型: | N 和 P 沟道 |

| FET 特点: | 逻辑电平门 |

| 漏极至源极电压(Vdss): | 20V |

| 电流 - 连续漏极(Id) @ 25° C: | 5.2A,3.4A |

| 开态Rds(最大)@ Id, Vgs @ 25° C: | 43 毫欧 @ 4A,4.5V |

| Id 时的 Vgs(th)(最大): | 1.2V @ 250µA |

| 闸电荷(Qg) @ Vgs: | 20nC @ 4.5V |

| 输入电容 (Ciss) @ Vds: | 1100pF @ 10V |

| 功率 - 最大: | 2W |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SOICN |

| 包装: | 带卷 (TR) |

�� �

�

NTMD2C02R2�

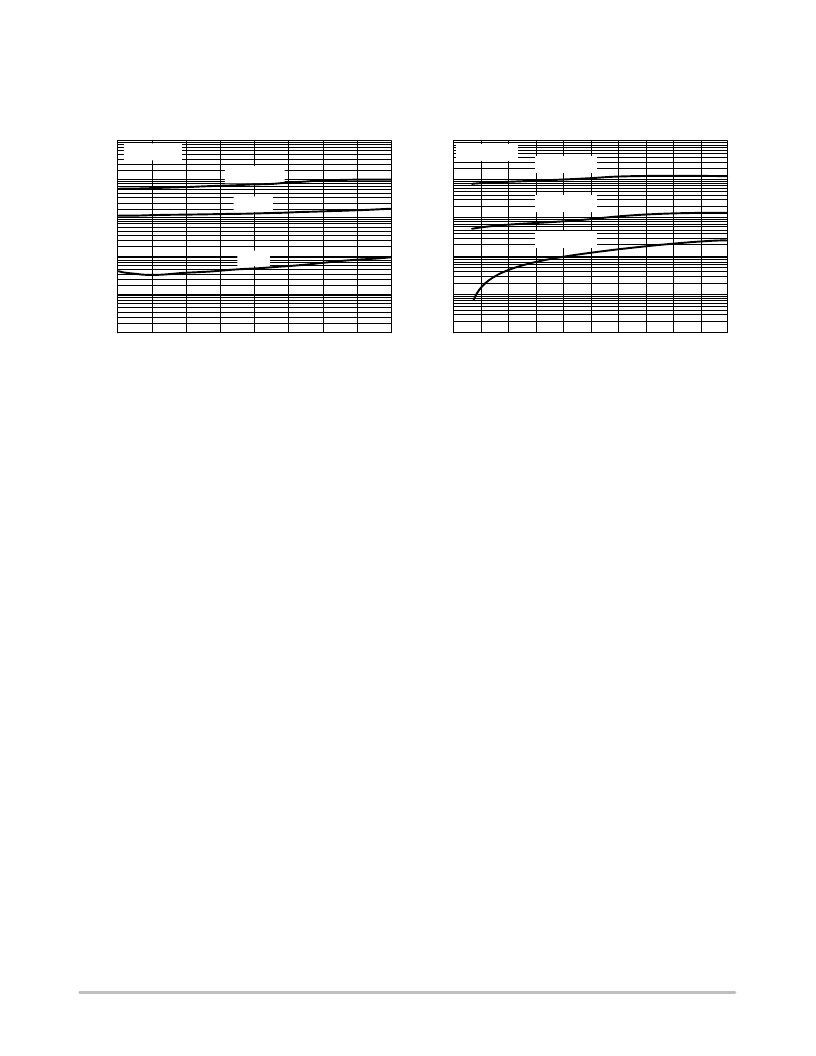

�TYPICAL� ELECTRICAL� CHARACTERISTICS�

�N� ?� Channel�

�P� ?� Channel�

�1000�

�100�

�10�

�V� GS� =� 0� V�

�T� J� =� 125� °� C�

�100� °� C�

�1000�

�100�

�10�

�V� GS� =� 0� V�

�T� J� =� 125� °� C�

�T� J� =� 100� °� C�

�T� J� =� 25� °� C�

�1�

�0.1�

�25� °� C�

�1�

�0.1�

�0.01�

�4�

�8�

�12�

�16�

�20�

�0.01�

�0�

�4� 8� 12� 16�

�20�

�V� DS� ,� DRAIN� ?� TO� ?� SOURCE� VOLTAGE� (VOLTS)�

�Figure� 11.� Drain� ?� To� ?� Source� Leakage�

�Current� versus� Voltage�

�?� V� DS,� DRAIN� ?� TO� ?� SOURCE� VOLTAGE� (VOLTS)�

�Figure� 12.� Drain� ?� To� ?� Source� Leakage�

�Current� versus� Voltage�

�POWER� MOSFET� SWITCHING�

�Switching� behavior� is� most� easily� modeled� and� predicted�

�by� recognizing� that� the� power� MOSFET� is� charge�

�controlled.� The� lengths� of� various� switching� intervals� (� D� t)�

�are� determined� by� how� fast� the� FET� input� capacitance� can�

�be� charged� by� current� from� the� generator.�

�The� published� capacitance� data� is� difficult� to� use� for�

�calculating� rise� and� fall� because� drain� ?� gate� capacitance�

�varies� greatly� with� applied� voltage.� Accordingly,� gate�

�charge� data� is� used.� In� most� cases,� a� satisfactory� estimate� of�

�average� input� current� (I� G(AV)� )� can� be� made� from� a�

�rudimentary� analysis� of� the� drive� circuit� so� that�

�t� =� Q/I� G(AV)�

�During� the� rise� and� fall� time� interval� when� switching� a�

�resistive� load,� V� GS� remains� virtually� constant� at� a� level�

�known� as� the� plateau� voltage,� V� SGP� .� Therefore,� rise� and� fall�

�times� may� be� approximated� by� the� following:�

�t� r� =� Q� 2� x� R� G� /(V� GG� ?� V� GSP� )�

�t� f� =� Q� 2� x� R� G� /V� GSP�

�where�

�V� GG� =� the� gate� drive� voltage,� which� varies� from� zero� to� V� GG�

�R� G� =� the� gate� drive� resistance�

�and� Q� 2� and� V� GSP� are� read� from� the� gate� charge� curve.�

�During� the� turn� ?� on� and� turn� ?� off� delay� times,� gate� current� is�

�not� constant.� The� simplest� calculation� uses� appropriate�

�values� from� the� capacitance� curves� in� a� standard� equation� for�

�voltage� change� in� an� RC� network.� The� equations� are:�

�The� capacitance� (C� iss� )� is� read� from� the� capacitance� curve� at�

�a� voltage� corresponding� to� the� off� ?� state� condition� when�

�calculating� t� d(on)� and� is� read� at� a� voltage� corresponding� to� the�

�on� ?� state� when� calculating� t� d(off)� .�

�At� high� switching� speeds,� parasitic� circuit� elements�

�complicate� the� analysis.� The� inductance� of� the� MOSFET�

�source� lead,� inside� the� package� and� in� the� circuit� wiring�

�which� is� common� to� both� the� drain� and� gate� current� paths,�

�produces� a� voltage� at� the� source� which� reduces� the� gate� drive�

�current.� The� voltage� is� determined� by� Ldi/dt,� but� since� di/dt�

�is� a� function� of� drain� current,� the� mathematical� solution� is�

�complex.� The� MOSFET� output� capacitance� also�

�complicates� the� mathematics.� And� finally,� MOSFETs� have�

�finite� internal� gate� resistance� which� effectively� adds� to� the�

�resistance� of� the� driving� source,� but� the� internal� resistance�

�is� difficult� to� measure� and,� consequently,� is� not� specified.�

�The� resistive� switching� time� variation� versus� gate�

�resistance� (Figures� 17� and� 18)� show� how� typical� switching�

�performance� is� affected� by� the� parasitic� circuit� elements.� If�

�the� parasitics� were� not� present,� the� slope� of� the� curves� would�

�maintain� a� value� of� unity� regardless� of� the� switching� speed.�

�The� circuit� used� to� obtain� the� data� is� constructed� to� minimize�

�common� inductance� in� the� drain� and� gate� circuit� loops� and�

�is� believed� readily� achievable� with� board� mounted�

�components.� Most� power� electronic� loads� are� inductive;� the�

�data� in� the� figures� is� taken� with� a� resistive� load,� which�

�approximates� an� optimally� snubbed� inductive� load.� Power�

�MOSFETs� may� be� safely� operated� into� an� inductive� load;�

�however,� snubbing� reduces� switching� losses.�

�t� d(on)� =� R� G� C� iss� In� [V� GG� /(V� GG� ?� V� GSP� )]�

�t� d(off)� =� R� G� C� iss� In� (V� GG� /V� GSP� )�

�http://onsemi.com�

�5�

�相关PDF资料 |

PDF描述 |

|---|---|

| NTMD2P01R2G | MOSFET PWR P-CHAN DUAL 16V 8SOIC |

| NTMD4184PFR2G | MOSFET P-CH 30V 2.3A 8-SOIC |

| NTMD4820NR2G | MOSFET N-CH DUAL 30V 4.9A 8-SOIC |

| NTMD4840NR2G | MOSFET N-CH DUAL 30V 4.5A 8-SOIC |

| NTMD4884NFR2G | MOSFET N-CH 30V 3.3A 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| NTMD2P01R2 | 功能描述:MOSFET -16V 2.3A Dual RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube |

| NTMD2P01R2G | 功能描述:MOSFET -16V 2.3A Dual P-Channel RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube |

| NTMD3N08 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TRANSISTOR | MOSFET | MATCHED PAIR | N-CHANNEL | 80V V(BR)DSS | SO |

| NTMD3N08/D | 制造商:未知厂家 制造商全称:未知厂家 功能描述:80 V Power MOSFET |

| NTMD3N08L | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TRANSISTOR | MOSFET | MATCHED PAIR | N-CHANNEL | 80V V(BR)DSS | SO |

发布紧急采购,3分钟左右您将得到回复。