- 您现在的位置:买卖IC网 > PDF目录98069 > S1R72V17B00A UNIVERSAL SERIAL BUS CONTROLLER, PBGA60 PDF资料下载

参数资料

| 型号: | S1R72V17B00A |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA60 |

| 封装: | 5 X 5 MM, 0.50 MM PITCH, PLASTIC, TFBGA-60 |

| 文件页数: | 30/45页 |

| 文件大小: | 3044K |

| 代理商: | S1R72V17B00A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

6. Functional Description

16

EPSON

S1R72V17*** Technical Manual (Rev.1.6)

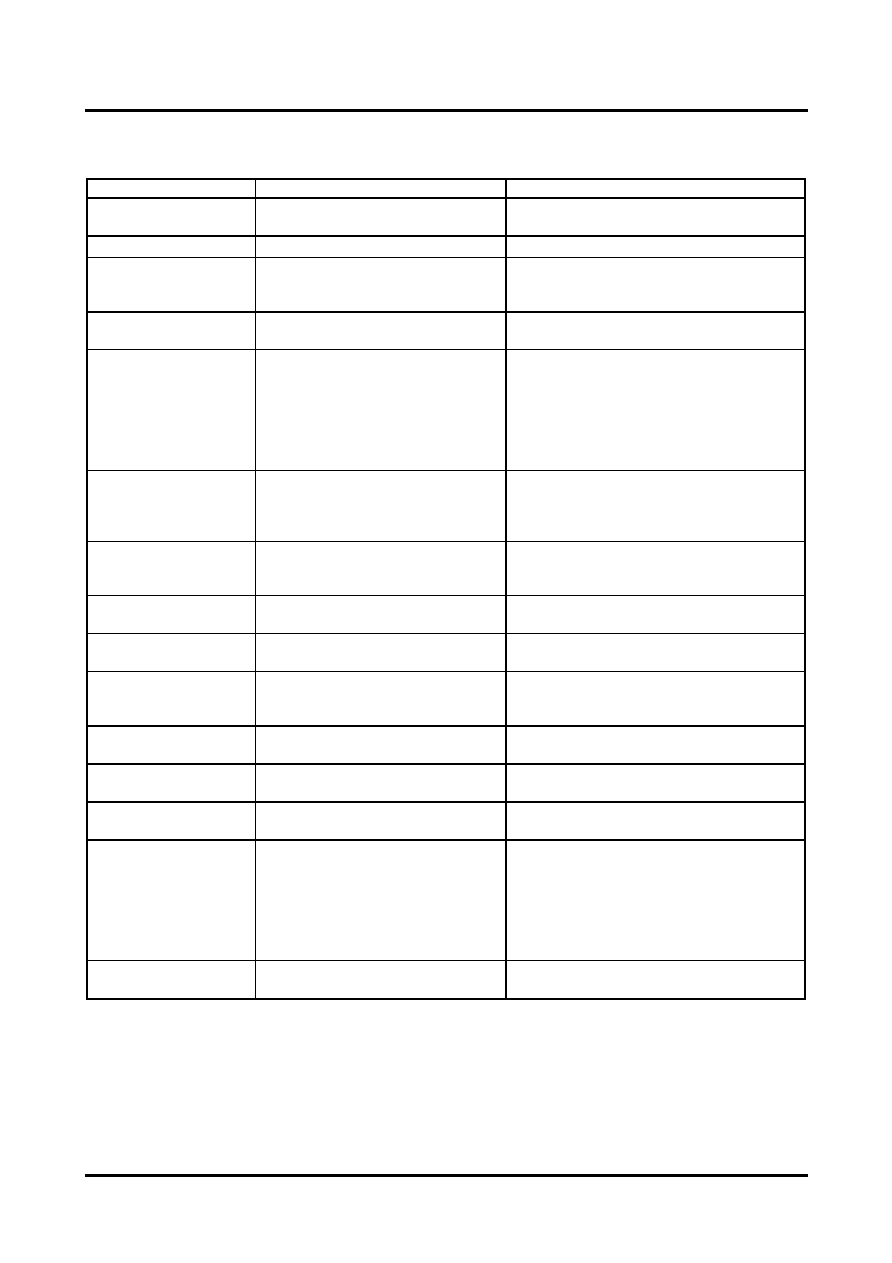

Table 6.7 Endpoint EP0 Control Items and Status

Item

Register/Bit

Description

Transaction direction

D_EP0Control.INxOUT

Sets the direction of transfer in the data and

status stages.

Descriptor reply enable

D_EP0Control.ReplyDescriptor

Invokes automatic descriptor response.

Descriptor reply address

D_DescAdrs_H, DescAdrs_L

Specifies the start address in FIFO of the data

to be returned by an automatic descriptor

response.

Descriptor size

D_DescSize_H, DescSize_L

Specifies the data quantity to be returned by an

automatic descriptor response.

Control protect

D_SETUP_Control.ProtectEP0

When this bit is set, the ForceNAK and

ForceSTALL bits in the EP0ControlIN and

EP0ControlOUT registers are protected against

access.

This bit is set in hardware by the LSI when a

RcvEP0SETUP status is flagged, and can be

cleared by a register access by the CPU.

Short packet transmit

enable

D_EP0ControlIN.EnShortPkt

Enables transmission of short packets less than

Max. packet size. This bit is cleared when the

IN transaction that transmitted a short packet is

completed.

Toggle sequence bit

D_EP0ControlIN.ToggleStat,

D_EP0ControlOUT.ToggleStat

Indicates the status of the toggle sequence bits.

These bits are automatically initialized by a

SETUP stage.

Toggle set

D_EP0ControlIN.ToggleSet,

D_EP0ControlOUT.ToggleSet

Sets the toggle sequence bits.

Toggle clear

D_EP0ControlIN.ToggleClr,

D_EP0ControlOUT.ToggleClr

Clears the toggle sequence bits.

Forced NAK response

D_EP0ControlIN.ForceNAK,

D_EP0ControlOUT.ForceNAK

Always responds with NAK for IN or OUT

(including PING) transactions irrespective of the

data quantity and free space in the FIFO.

STALL response

D_EP0ControlIN.ForceSTALL,

D_EP0ControlOUT.ForceSTALL

Responds with STALL for IN or OUT (including

PING) transactions.

Automatic ForceNAK set

D_EP0ControlOUT.AutoForceNAK

Sets the EP0ControlOUT.ForceNAK bit each

time an OUT transaction is completed.

SETUP receive status

USB_DeviceIntStat.RcvEP0SETUP

Indicates that a SETUP transaction has been

executed.

Transaction status

D_EP0IntStat.OUT_ShortACK,

D_EP0IntStat.IN_TranACK,

D_EP0IntStat.OUT_TranACK,

D_EP0IntStat.IN_TranNAK,

D_EP0IntStat.OUT_TranNAK,

D_EP0IntStat.IN_TranErr,

D_EP0IntStat.OUT_TranErr

Indicates the result of a transaction.

Descriptor reply data

stage end status

D_FIFO_IntStat.DescriptorCmp

Indicates that the data stage of an automatic

descriptor response has ended.

相关PDF资料 |

PDF描述 |

|---|---|

| S1R72V18B10 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA121 |

| S1R72V27B05 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA60 |

| S2024B-8 | 32-BIT, DSP-CROSSBAR SWITCH, PQFP196 |

| S2025A | 32-BIT, DSP-CROSSBAR SWITCH, PQFP196 |

| S2025C-15 | 32-BIT, DSP-CROSSBAR SWITCH, PQFP196 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S1R72V17B00A20 | 制造商:Epson Electronics America Inc 功能描述:USB HS HOST/DEVICE CONTROLLER, |

| S1R72V18 | 制造商:EPSON 制造商全称:EPSON 功能描述:Built-in pull-down resistor for downstream ports (no external circuit required) |

| S1R72V27 | 制造商:EPSON 制造商全称:EPSON 功能描述:Built-in pull-down resistor for downstream ports (no external circuit required) |

| S1R77081F | 制造商:EPSON 制造商全称:EPSON 功能描述:RSDS Transmitter/Receiver |

| S1R8ADMTBK | 制造商:Hubbell Wiring Device-Kellems 功能描述:S1R FRPT 8 ABANDONMENT PLATE |

发布紧急采购,3分钟左右您将得到回复。