- 您现在的位置:买卖IC网 > PDF目录98069 > S1R72V17B00A UNIVERSAL SERIAL BUS CONTROLLER, PBGA60 PDF资料下载

参数资料

| 型号: | S1R72V17B00A |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA60 |

| 封装: | 5 X 5 MM, 0.50 MM PITCH, PLASTIC, TFBGA-60 |

| 文件页数: | 32/45页 |

| 文件大小: | 3044K |

| 代理商: | S1R72V17B00A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

6. Functional Description

18

EPSON

S1R72V17*** Technical Manual (Rev.1.6)

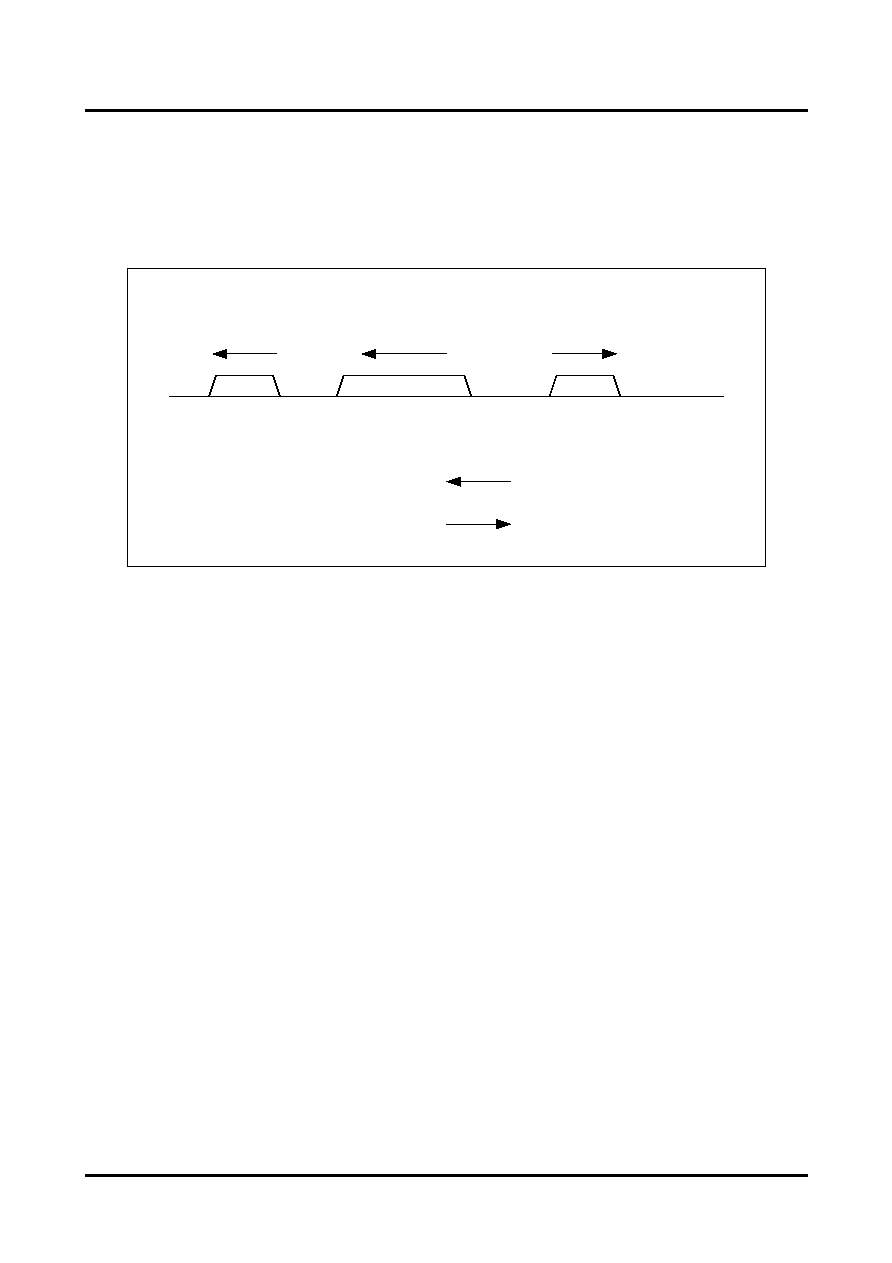

Fig. 6.1 shows how a SETUP transaction is performed in device mode. In (a), the host issues a

SETUP token addressed to the endpoint EP0 of this node. In (b), the host continues to send an 8

bytes long data packet. The LSI writes this data to the D_EP0SETUP_0 to D_EP0SETUP_7

registers. In (c), the LSI automatically returns an ACK response. Furthermore, it sets up the

registers to be automatically set and issues a status to the firmware.

SETUP

DATA

ACK

c

ab

Host to Device

Device to Host

Fig. 6.1 SETUP transaction in device mode

6.2.2.2

Bulk/Interrupt OUT Transactions

In a bulk/interrupt OUT transaction, the LSI starts receiving data if the FIFO has a free space equal

to or greater than Max. packet size.

When all bytes of data are received correctly in a bulk/interrupt OUT transaction, the LSI completes

the transaction and returns an ACK or a NYET response. It then issues an OUT_TranACK status

for the corresponding endpoint (D_EPx{x=0, a-e}IntStat.OUT_TranACK bit) to the firmware. It

also updates the FIFO and assuming that data has all been received, reserves a storage area.

Furthermore, when all data bytes of a short packet have been received in a bulk/interrupt OUT

transaction, the LSI issues an OUT_ShortACK status (D_EPx{x=0, a-e}IntStat.OUT_ShortACK

bit), in addition to the transaction-complete processing described above. Furthermore, if the

D_EPx{x=0, a-e}Control.DisAF_NAK_Short bit is cleared, the LSI sets the

D_EPx{x=a-e}ForceNAK bit for the endpoint.

If a toggle mismatch occurs in a bulk/interrupt OUT transaction, the LSI responds with ACK for the

transaction but does not issue a status. The FIFO is not updated.

If an error occurs in a bulk/interrupt OUT transaction, the LSI does not respond for the transaction.

In this case, it issues an OUT_TranErr status (D_EPx{x=0, a-e}IntStat.OUT_TranErr bit). The

FIFO is not updated.

If all bytes of data could not be received in a bulk/interrupt OUT transaction, the LSI responds with

NAK for the transaction. It also issues an OUT_TranNAK status (D_EPx{x=0,

a-e}IntStat.OUT_TranNAK bit). The FIFO is not updated.

相关PDF资料 |

PDF描述 |

|---|---|

| S1R72V18B10 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA121 |

| S1R72V27B05 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA60 |

| S2024B-8 | 32-BIT, DSP-CROSSBAR SWITCH, PQFP196 |

| S2025A | 32-BIT, DSP-CROSSBAR SWITCH, PQFP196 |

| S2025C-15 | 32-BIT, DSP-CROSSBAR SWITCH, PQFP196 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S1R72V17B00A20 | 制造商:Epson Electronics America Inc 功能描述:USB HS HOST/DEVICE CONTROLLER, |

| S1R72V18 | 制造商:EPSON 制造商全称:EPSON 功能描述:Built-in pull-down resistor for downstream ports (no external circuit required) |

| S1R72V27 | 制造商:EPSON 制造商全称:EPSON 功能描述:Built-in pull-down resistor for downstream ports (no external circuit required) |

| S1R77081F | 制造商:EPSON 制造商全称:EPSON 功能描述:RSDS Transmitter/Receiver |

| S1R8ADMTBK | 制造商:Hubbell Wiring Device-Kellems 功能描述:S1R FRPT 8 ABANDONMENT PLATE |

发布紧急采购,3分钟左右您将得到回复。