参数资料

| 型号: | TMS320DM647ZUT7 |

| 厂商: | Texas Instruments |

| 文件页数: | 88/190页 |

| 文件大小: | 0K |

| 描述: | IC DGTL MEDIA PROC 529-FCBGA |

| 标准包装: | 84 |

| 系列: | TMS320DM64x, DaVinci™ |

| 类型: | 定点 |

| 接口: | 主机接口,I²C,McASP,PCI,SPI,UART |

| 时钟速率: | 720MHz |

| 非易失内存: | ROM(64 kB) |

| 芯片上RAM: | 320kB |

| 电压 - 输入/输出: | 1.8V,3.3V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 529-BFBGA,FCBGA |

| 供应商设备封装: | 529-FCBGA(19x19) |

| 包装: | 托盘 |

| 其它名称: | 296-34539-5 TMS320DM647ZUT7-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页当前第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页

SPRS372H – MAY 2007 – REVISED APRIL 2012

6.23 General-Purpose Input/Output (GPIO)

The GPIO peripheral provides general-purpose pins that can be configured as either inputs or outputs.

When configured as an output, a write to an internal register can control the state driven on the output pin.

When configured as an input, the state of the input is detectable by reading the state of an internal

register. In addition, the GPIO peripheral can produce CPU interrupts and EDMA events in different

interrupt/event generation modes. The GPIO peripheral provides generic connections to external devices.

The GPIO pins are grouped into banks of 16 pins per bank (i.e., bank 0 consists of GPIO [0:15]).

The GPIO peripheral supports the following:

Up to 3.3-V GPIO pins

Interrupts:

–

Up to 16 unique GPIO[0:15] interrupts from Bank 0

–

One GPIO bank (aggregated) interrupt signal from the GPIOs in Bank 1

–

Interrupts can be triggered by rising and/or falling edge, specified for each interrupt capable GPIO

signal

DMA events:

–

Up to 10 unique GPIO DMA events from Bank 0

Set/clear functionality: Firmware writes 1 to corresponding bit position(s) to set or to clear GPIO

signal(s). This allows multiple firmware processes to toggle GPIO output signals without critical section

protection (disable interrupts, program GPIO, re-enable interrupts, to prevent context switching to

anther process during GPIO programming).

Separate Input/Output registers

Output register in addition to set/clear so that, if preferred by firmware, some GPIO output signals can

be toggled by direct write to the output register(s).

Output register, when read, reflects output drive status. This, in addition to the input register reflecting

pin status and open-drain I/O cell, allows wired logic be implemented.

The memory map for the GPIO registers is shown in Table 6-95.

For more detailed information on GPIOs, see the TMS320DM647/DM648 DSP General-Purpose

Input/Output (GPIO) User's Guide (literature number SPRUEK7).

6.23.1 GPIO Peripheral Register Descriptions

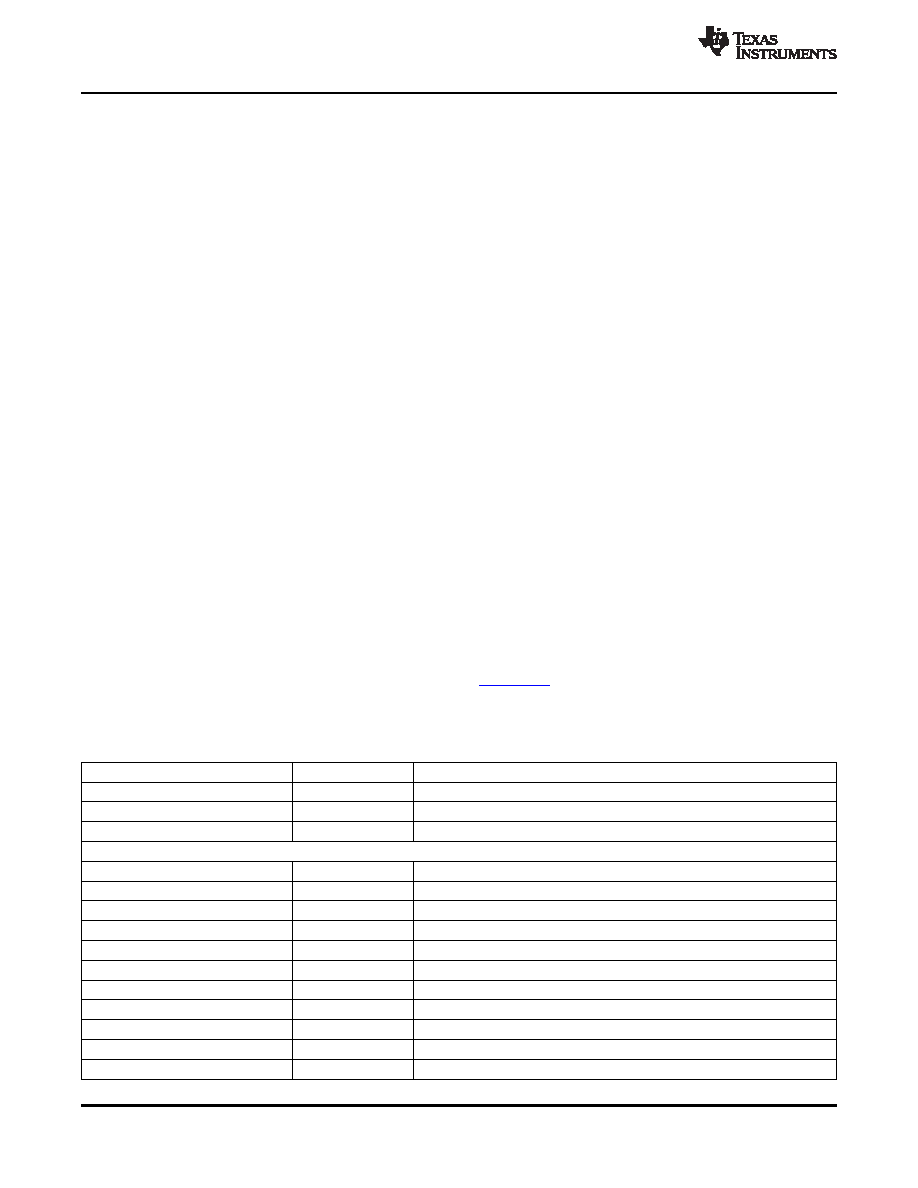

Table 6-95. GPIO Registers

HEX ADDRESS RANGE

ACRONYM

REGISTER NAME

0x0204 8000

PID

Peripheral Identification Register

0x0204 8004

-

Reserved

0x0204 8008

BINTEN

GPIO interrupt per-bank enable

GPIO Banks 0 and 1

0x0204 800C

-

Reserved

0x0204 8010

DIR

GPIO Banks 0 and 1 Direction Register (GPIO[0:31])

0x0204 8014

OUT_DATA

GPIO Banks 0 and 1 Output Data Register (GPIO[0:31])

0x0204 8018

SET_DATA

GPIO Banks 0 and 1 Set Data Register (GPIO[0:31])

0x0204 801C

CLR_DATA

GPIO Banks 0 and 1 Clear data for banks 0 and 1 (GPIO[0:31])

0x0204 8020

IN_DATA

GPIO Banks 0 and 1 Input Data Register (GPIO[0:31])

0x0204 8024

SET_RIS_TRIG

GPIO Banks 0 and 1 Set Rising Edge Interrupt Register (GPIO[0:31])

0x0204 8028

CLR_RIS_TRIG

GPIO Banks 0 and 1 Clear Rising Edge Interrupt Register (GPIO[0:31])

0x0204 802C

SET_FAL_TRIG

GPIO Banks 0 and 1 Set Falling Edge Interrupt Register (GPIO[0:31])

0x0204 8030

CLR_FAL_TRIG

GPIO Banks 0 and 1 Clear Falling Edge Interrupt Register (GPIO[0:31])

0x0204 8034

INSTAT

GPIO Banks 0 and 1 Interrupt Status Register (GPIO[0:31])

178

Peripheral Information and Electrical Specifications

Copyright 2007–2012, Texas Instruments Incorporated

Product Folder Link(s): TMS320DM647 TMS320DM648

相关PDF资料 |

PDF描述 |

|---|---|

| TMS320VC5409GGU100 | IC DIG SIG PROCESSOR 144-BGA |

| TMS470R1A384PZQ | IC RISC MCU 384K FLASH 100-LQFP |

| TMX320DM365BZCE | IC DIGITAL MEDIA SOC 338NFBGA |

| TMX320F28069UPFPA | IC MCU 32BIT 128KB FLASH 80HTQFP |

| TPS2371PWRG4 | IC PWR INTRFCE SW FOR POE 8TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMS320DM647ZUT9 | 功能描述:数字信号处理器和控制器 - DSP, DSC Dig Media Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| TMS320DM647ZUTA8 | 功能描述:数字信号处理器和控制器 - DSP, DSC Digital Media Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| TMS320DM647ZUTD1 | 制造商:Texas Instruments 功能描述:- Trays |

| TMS320DM647ZUTD7 | 功能描述:数字信号处理器和控制器 - DSP, DSC Digital Media Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| TMS320DM647ZUTD9 | 功能描述:数字信号处理器和控制器 - DSP, DSC Digital Media Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。