- 您现在的位置:买卖IC网 > PDF目录297644 > UPSD3253B-40T6 (STMICROELECTRONICS) 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP52 PDF资料下载

参数资料

| 型号: | UPSD3253B-40T6 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP52 |

| 封装: | PLASTIC, TQFP-52 |

| 文件页数: | 173/189页 |

| 文件大小: | 1638K |

| 代理商: | UPSD3253B-40T6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页当前第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页

Obsolete

Product(s)

- Obsolete

Product(s)

I2C interface

UPSD3254A, UPSD3254BV, UPSD3253B, UPSD3253BV

15

I2C interface

There are two serial I2C ports implemented in the UPSD325xx devices.

The serial port supports the twin line I2C-bus, consists of a data line (SDAx) and a clock line

(SCLx). Depending on the configuration, the SDA and SCL lines may require pull-up

resistors.

●

SDA1, SCL1: the serial port line for DDC Protocol

●

SDA2, SCL2: the serial port line for general I2C bus connection

In both I2C interfaces, these lines also function as I/O port lines as follows.

●

SDA1 / P4.0, SCL1 / P4.1, SDA2 / P3.6, SCL2 / P3.7

The system is unique because data transport, clock generation, address recognition and

bus control arbitration are all controlled by hardware.

The I2C serial I/O has complete autonomy in byte handling and operates in 4 modes.

●

Master transmitter

●

Master receiver

●

Slave transmitter

●

Slave receiver

These functions are controlled by the SFRs.

●

SxCON: the control of byte handling and the operation of 4 mode.

●

SxSTA: the contents of its register may also be used as a vector to various service

routines.

●

SxDAT: data shift register.

●

SxADR: slave address register. Slave address recognition is performed by On-Chip

H/W.

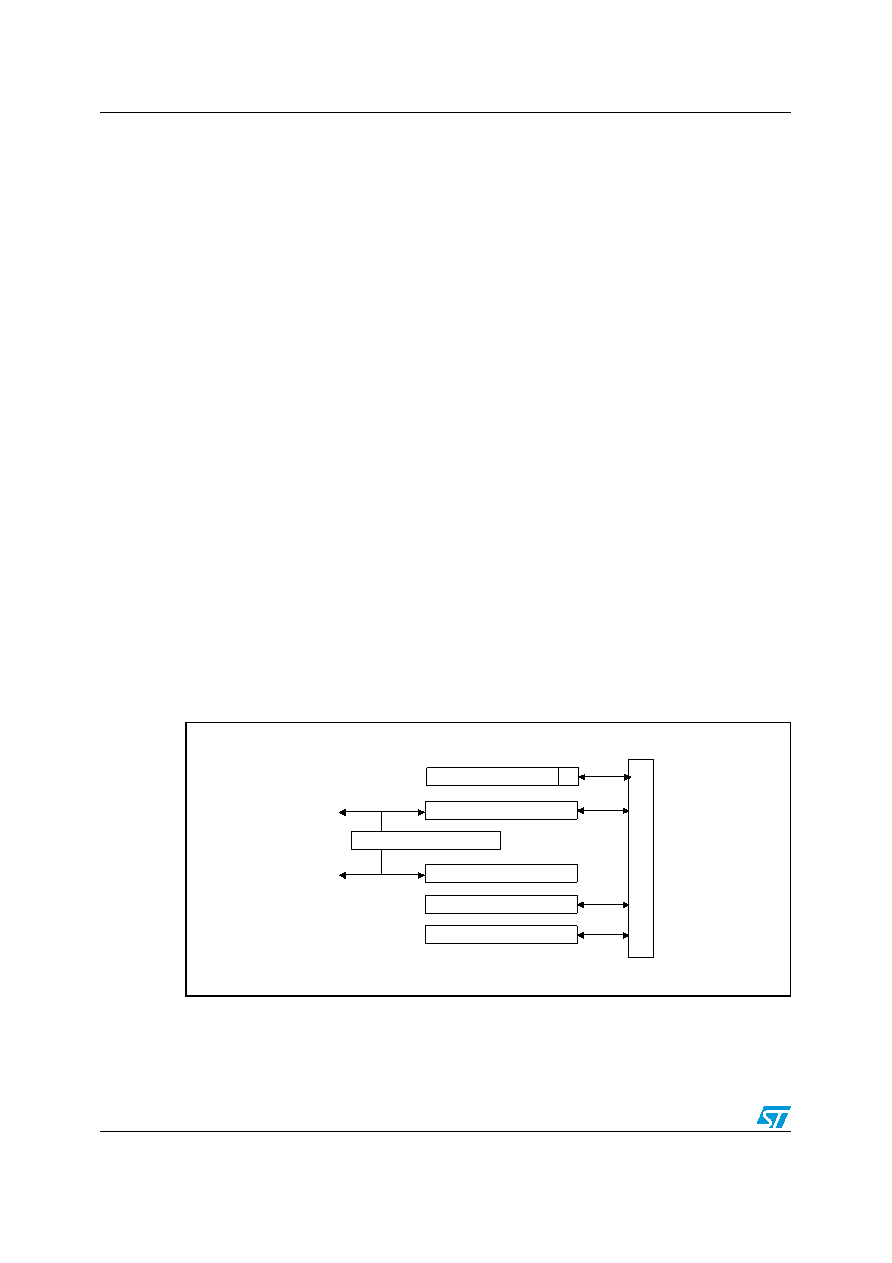

Figure 38.

Block diagram of the I2C bus serial I/O

AI06649

SCLx

SDAx

Bus Clock Generator

Arbitration and Sync. Logic

Shift Register

Status Register

70

Slave Address

70

Control Register

70

Internal

Bus

相关PDF资料 |

PDF描述 |

|---|---|

| UPSD3334D-40U6 | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP80 |

| US1001FL | 0.5 A, 100 V, SILICON, SIGNAL DIODE |

| US1A-HE3 | 1 A, 50 V, SILICON, SIGNAL DIODE, DO-214AC |

| US1B-HE3 | 1 A, 100 V, SILICON, SIGNAL DIODE, DO-214AC |

| US1G-HE3 | 1 A, 400 V, SILICON, SIGNAL DIODE, DO-214AC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| UPSD3253B-40T6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

| UPSD3253B-40U1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

| UPSD3253B-40U1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

| UPSD3253B-40U6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

| UPSD3253B-40U6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

发布紧急采购,3分钟左右您将得到回复。