参数资料

| 型号: | XC2S400E-6FGG456C |

| 厂商: | Xilinx Inc |

| 文件页数: | 17/108页 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-IIE FPGA 400K 456FBGA |

| 产品变化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 标准包装: | 60 |

| 系列: | Spartan®-IIE |

| LAB/CLB数: | 2400 |

| 逻辑元件/单元数: | 10800 |

| RAM 位总计: | 163840 |

| 输入/输出数: | 329 |

| 门数: | 400000 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 456-BBGA |

| 供应商设备封装: | 456-FBGA |

| 其它名称: | 122-1327 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

16

DS077-2 (v3.0) August 9, 2013

Product Specification

Spartan-IIE FPGA Family: Functional Description

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

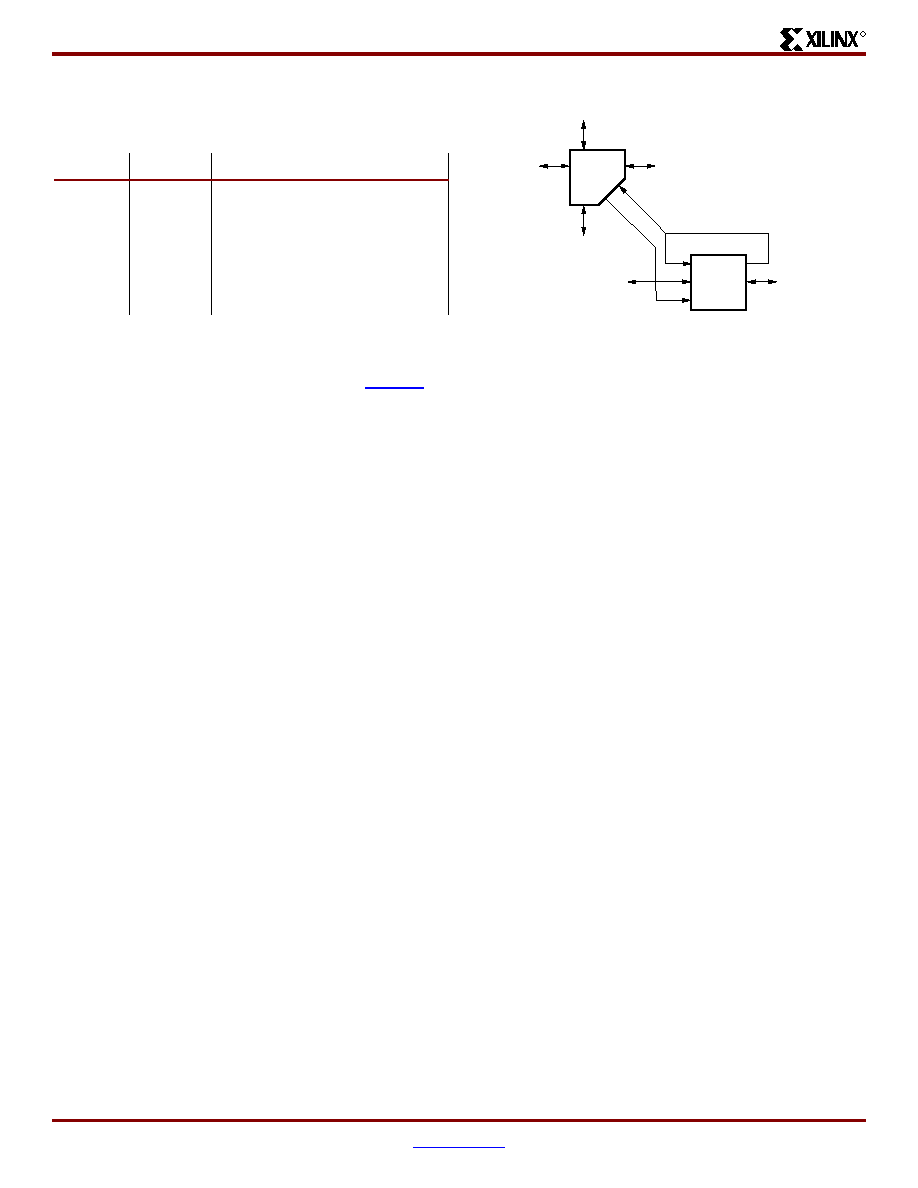

Table 7 shows the depth and width aspect ratios for the

block RAM.

The Spartan-IIE FPGA block RAM also includes dedicated

routing to provide an efficient interface with both CLBs and

other block RAMs. See Xilinx Application Note XAPP173 for

more information on block RAM.

Programmable Routing

It is the longest delay path that limits the speed of any

design. Consequently, the Spartan-IIE FPGA routing archi-

tecture and its place-and-route software were defined jointly

to minimize long-path delays and yield the best system per-

formance.

The joint optimization also reduces design compilation

times because the architecture is software-friendly. Design

cycles are correspondingly reduced due to shorter design

iteration times.

The software automatically uses the best available routing

based on user timing requirements. The details are pro-

vided here for reference.

Local Routing

The local routing resources, as shown in Figure 9, provide

the following three types of connections:

Interconnections among the LUTs, flip-flops, and

General Routing Matrix (GRM), described below.

Internal CLB feedback paths that provide high-speed

connections to LUTs within the same CLB, chaining

them together with minimal routing delay

Direct paths that provide high-speed connections

between horizontally adjacent CLBs, eliminating the

delay of the GRM

General Purpose Routing

Most Spartan-IIE FPGA signals are routed on the general

purpose routing, and consequently, the majority of intercon-

nect resources are associated with this level of the routing

hierarchy. The general routing resources are located in hor-

izontal and vertical routing channels associated with the

rows and columns of CLBs. The general-purpose routing

resources are listed below.

Adjacent to each CLB is a General Routing Matrix

(GRM). The GRM is the switch matrix through which

horizontal and vertical routing resources connect, and

is also the means by which the CLB gains access to

the general purpose routing.

24 single-length lines route GRM signals to adjacent

GRMs in each of the four directions.

96 buffered Hex lines route GRM signals to other

GRMs six blocks away in each one of the four

directions. Organized in a staggered pattern, Hex lines

may be driven only at their endpoints. Hex-line signals

can be accessed either at the endpoints or at the

midpoint (three blocks from the source). One third of

the Hex lines are bidirectional, while the remaining

ones are unidirectional.

12 Longlines are buffered, bidirectional wires that

distribute signals across the device quickly and

efficiently. Vertical Longlines span the full height of the

device, and horizontal ones span the full width of the

device.

I/O Routing

Spartan-IIE devices have additional routing resources

around their periphery that form an interface between the

CLB array and the IOBs. This additional routing, called the

VersaRing routing, facilitates pin-swapping and pin-lock-

ing, such that logic redesigns can adapt to existing PCB lay-

outs. Time-to-market is reduced, since PCBs and other

system components can be manufactured while the logic

design is still in progress.

Table 7: Block RAM Port Aspect Ratios

Width

Depth

ADDR Bus

Data Bus

1

4096

ADDR<11:0>

DATA<0>

2

2048

ADDR<10:0>

DATA<1:0>

4

1024

ADDR<9:0>

DATA<3:0>

8

512

ADDR<8:0>

DATA<7:0>

16

256

ADDR<7:0>

DATA<15:0>

Figure 9: Spartan-IIE Local Routing

DS001_06_032300

CLB

GRM

To

Adjacent

GRM

To Adjacent

GRM

Direct

Connection

To Adjacent

CLB

To Adjacent

GRM

To Adjacent

GRM

Direct Connection

To Adjacent

CLB

相关PDF资料 |

PDF描述 |

|---|---|

| XA6SLX100-2FGG484I | IC FPGA SPARTAN 6 484FGGBGA |

| 25LC640T-E/SN | IC EEPROM 64KBIT 2MHZ 8SOIC |

| SST25VF020B-80-4C-SAE-T | IC FLASH SER 2MB 80MHZ SPI 8SOIC |

| XC6SLX100-N3FGG484I | IC FPGA SPARTAN-6 484FPGA |

| SST25LF020A-33-4C-SAE | IC FLASH SER 2MB 33HZ SPI 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2S400E-6FGG456I | 制造商:Xilinx 功能描述:FPGA SPARTAN-IIE 400K GATES 10800 CELLS 357MHZ 1.8V 456FBGA - Trays |

| XC2S400E-6FGG676C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6FGG676I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6FT256C | 功能描述:IC SPARTAN-IIE FPGA 400K 256FTBG RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC2S400E-6FT256I | 制造商:Xilinx 功能描述:FPGA SPARTAN-IIE 400K GATES 10800 CELLS 357MHZ 1.8V 256FTBGA - Trays |

发布紧急采购,3分钟左右您将得到回复。