参数资料

| 型号: | XC2S400E-6FGG456C |

| 厂商: | Xilinx Inc |

| 文件页数: | 58/108页 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-IIE FPGA 400K 456FBGA |

| 产品变化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 标准包装: | 60 |

| 系列: | Spartan®-IIE |

| LAB/CLB数: | 2400 |

| 逻辑元件/单元数: | 10800 |

| RAM 位总计: | 163840 |

| 输入/输出数: | 329 |

| 门数: | 400000 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 456-BBGA |

| 供应商设备封装: | 456-FBGA |

| 其它名称: | 122-1327 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

DS077-4 (v3.0) August 9, 2013

53

Product Specification

2001–-2013 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other

trademarks are the property of their respective owners.

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Introduction

This section describes how the various pins on a

Spartan-IIE FPGA connect within the supported

component packages, and provides device-specific thermal

characteristics. Spartan-IIE FPGAs are available in both

standard and Pb-free, RoHS versions of each package, with

the Pb-free version adding a “G” to the middle of the

package code. Except for the thermal characteristics, all

information for the standard package applies equally to the

Pb-free package.

Pin Types

Most pins on a Spartan-IIE FPGA are general-purpose,

user-defined I/O pins. There are, however, different

functional types of pins on Spartan-IIE FPGA packages, as

outlined below.

Spartan-IIE FPGA Family:

Pinout Tables

DS077-4 (v3.0) August 9, 2013

0

Product Specification

R

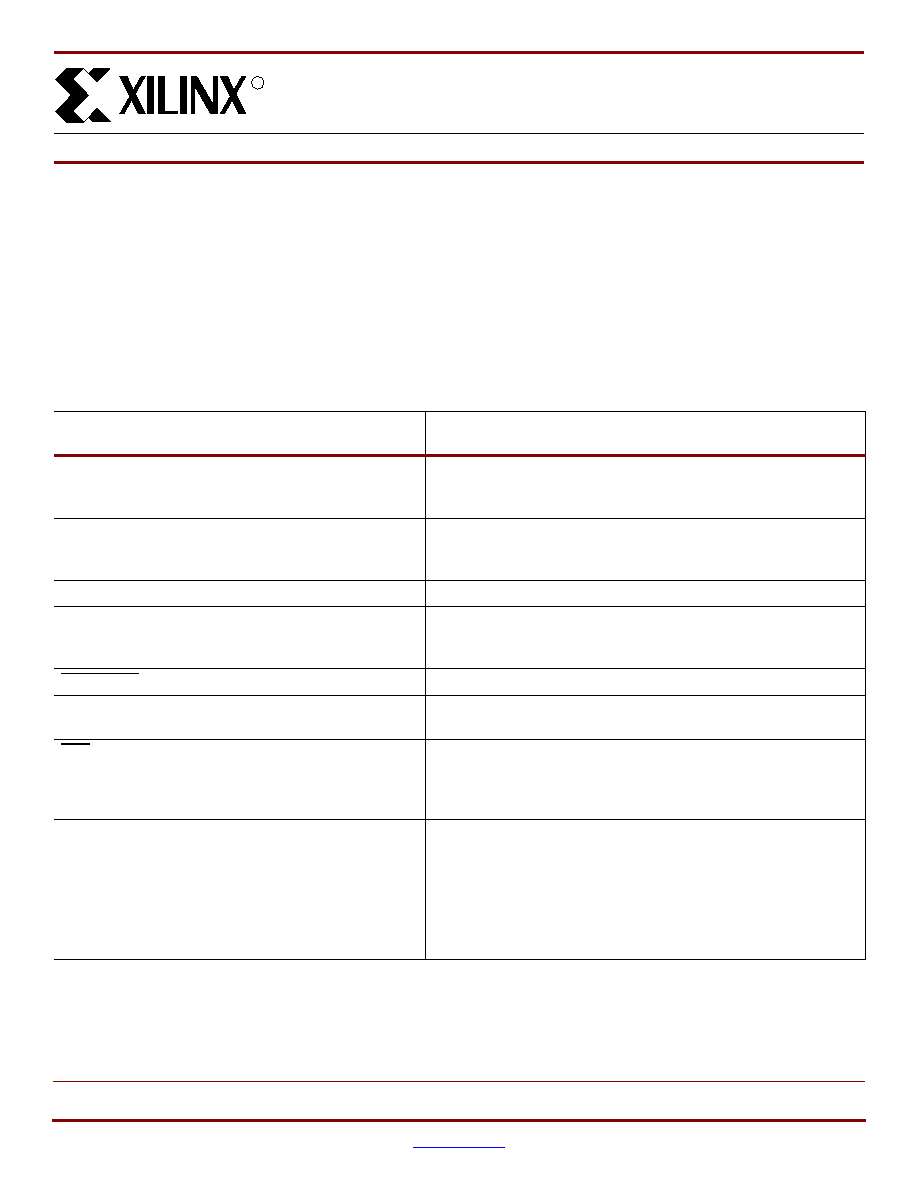

Pin Definitions

Pad Name

Dedicated

Pin

Direction

Description

GCK0, GCK1, GCK2,

GCK3

No

Input

Clock input pins that connect to Global Clock buffers or DLL

inputs. These pins become user inputs when not needed for

clocks.

DLL

No

Input

Clock input pins that connect to DLL input or feedback clocks.

Differential clock input (N input of pair) when paired with adjacent

GCK input. Becomes a user I/O when not needed for clocks.

M0, M1, M2

Yes

Input

Mode pins used to specify the configuration mode.

CCLK

Yes

Input or Output

The configuration Clock I/O pin. It is an input for Slave Parallel

and Slave Serial modes, and output in Master Serial mode. After

configuration, it is an input only with Don’t Care logic levels.

PROGRAM

Yes

Input

Initiates a configuration sequence when asserted Low.

DONE

Yes

Bidirectional

Indicates that configuration loading is complete, and that the

start-up sequence is in progress. The output may be open drain.

INIT

No

Bidirectional

(Open-drain)

When Low, indicates that the configuration memory is being

cleared. Goes High to indicate the end of initialization. Goes back

Low to indicate a CRC error. This pin becomes a user I/O after

configuration.

DOUT/BUSY

No

Output

In Slave Parallel mode, BUSY controls the rate at which

configuration data can be loaded. It is not needed below 50 MHz.

This pin becomes a user I/O after configuration unless the Slave

Parallel port is retained.

In serial modes, DOUT provides configuration data to

downstream devices in a daisy-chain. This pin becomes a user

I/O after configuration.

相关PDF资料 |

PDF描述 |

|---|---|

| XA6SLX100-2FGG484I | IC FPGA SPARTAN 6 484FGGBGA |

| 25LC640T-E/SN | IC EEPROM 64KBIT 2MHZ 8SOIC |

| SST25VF020B-80-4C-SAE-T | IC FLASH SER 2MB 80MHZ SPI 8SOIC |

| XC6SLX100-N3FGG484I | IC FPGA SPARTAN-6 484FPGA |

| SST25LF020A-33-4C-SAE | IC FLASH SER 2MB 33HZ SPI 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2S400E-6FGG456I | 制造商:Xilinx 功能描述:FPGA SPARTAN-IIE 400K GATES 10800 CELLS 357MHZ 1.8V 456FBGA - Trays |

| XC2S400E-6FGG676C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6FGG676I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6FT256C | 功能描述:IC SPARTAN-IIE FPGA 400K 256FTBG RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC2S400E-6FT256I | 制造商:Xilinx 功能描述:FPGA SPARTAN-IIE 400K GATES 10800 CELLS 357MHZ 1.8V 256FTBGA - Trays |

发布紧急采购,3分钟左右您将得到回复。