参数资料

| 型号: | XC2S400E-6FGG456C |

| 厂商: | Xilinx Inc |

| 文件页数: | 51/108页 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-IIE FPGA 400K 456FBGA |

| 产品变化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 标准包装: | 60 |

| 系列: | Spartan®-IIE |

| LAB/CLB数: | 2400 |

| 逻辑元件/单元数: | 10800 |

| RAM 位总计: | 163840 |

| 输入/输出数: | 329 |

| 门数: | 400000 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 456-BBGA |

| 供应商设备封装: | 456-FBGA |

| 其它名称: | 122-1327 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页当前第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

DS077-3 (v3.0) August 9, 2013

47

Product Specification

Spartan-IIE FPGA Family: DC and Switching Characteristics

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

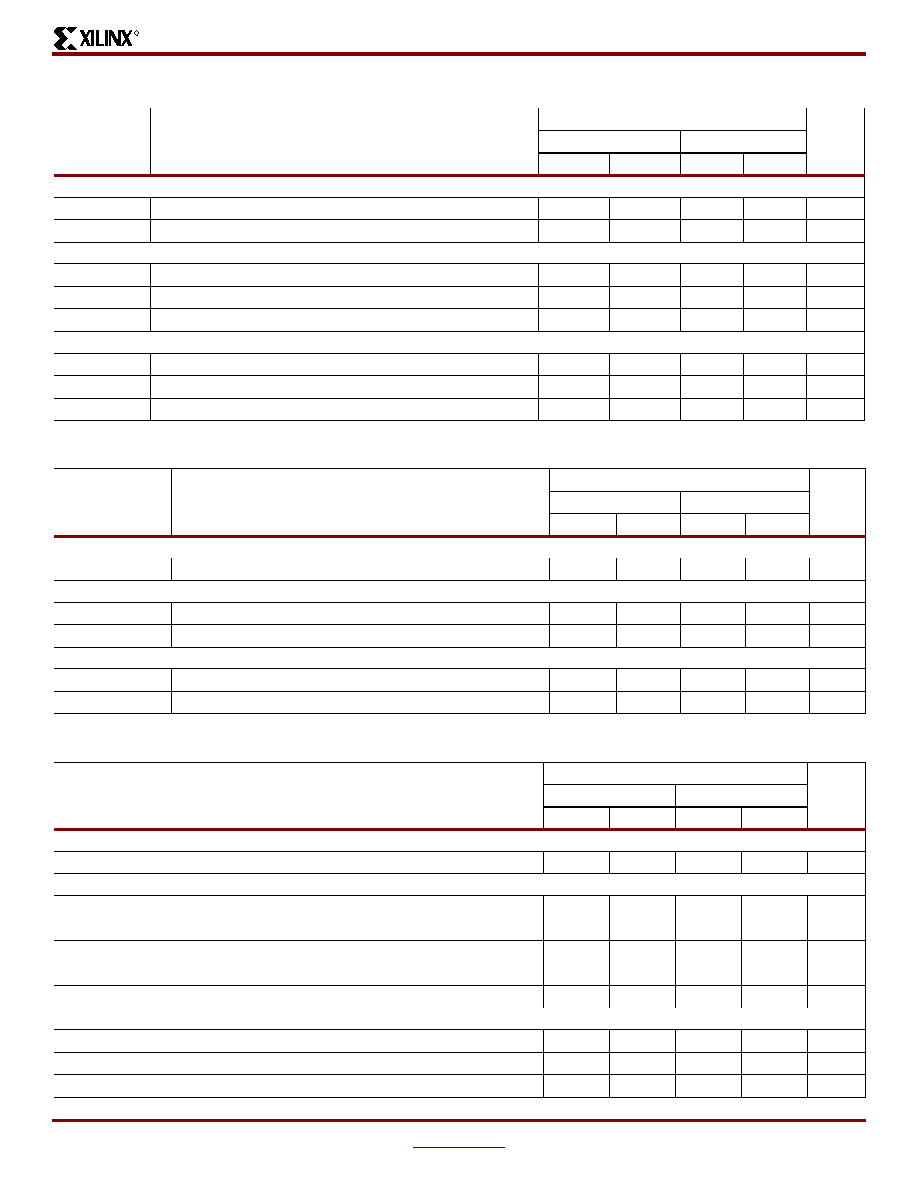

CLB Distributed RAM Switching Characteristics

CLB Shift Register Switching Characteristics

Block RAM Switching Characteristics

Symbol

Description

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Sequential Delays

TSHCKO16

Clock CLK to X/Y outputs (WE active, 16 x 1 mode)

0.6

1.5

0.6

1.7

ns

TSHCKO32

Clock CLK to X/Y outputs (WE active, 32 x 1 mode)

0.8

1.9

0.8

2.1

ns

Setup/Hold Times with Respect to Clock CLK

TAS / TAH

F/G address inputs

0.42 / 0

-

0.5 / 0

-

ns

TDS / TDH

BX/BY data inputs (DIN)

0.53 / 0

-

0.6 / 0

-

ns

TWS / TWH

CE input (WS)

0.7 / 0

-

0.8 / 0

-

ns

Clock CLK

TWPH

Pulse width, High

2.1

-

2.4

-

ns

TWPL

Pulse width, Low

2.1

-

2.4

-

ns

TWC

Clock period to meet address write cycle time

4.2

-

4.8

-

ns

Symbol

Description

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Sequential Delays

TREG

Clock CLK to X/Y outputs

1.2

2.9

1.2

3.2

ns

Setup/Hold Times with Respect to Clock CLK

TSHDICK

BX/BY data inputs (DIN)

0.53 / 0

-

0.6 / 0

-

ns

TSHCECK

CE input (WS)

0.7 / 0

-

0.8 / 0

-

ns

Clock CLK

TSRPH

Pulse width, High

2.1

-

2.4

-

ns

TSRPL

Pulse width, Low

2.1

-

2.4

-

ns

Symbol

Description

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Sequential Delays

TBCKO

Clock CLK to DOUT output

0.6

3.1

0.6

3.5

ns

Setup/Hold Times with Respect to Clock CLK

TBACK / TBCKA

ADDR inputs

1.0 / 0

-

1.1 / 0

-

ns

TBDCK/ TBCKD

DIN inputs

1.0 / 0

-

1.1 / 0

-

ns

TBECK/ TBCKE

EN inputs

2.2 / 0

-

2.5 / 0

-

ns

TBRCK/ TBCKR

RST input

2.1 / 0

-

2.3 / 0

-

ns

TBWCK/ TBCKW

WEN input

2.0 / 0

-

2.2 / 0

-

ns

Clock CLK

TBPWH

Pulse width, High

1.4

-

1.5

-

ns

TBPWL

Pulse width, Low

1.4

-

1.5

-

ns

TBCCS

CLKA -> CLKB setup time for different ports

2.7

-

3.0

-

ns

相关PDF资料 |

PDF描述 |

|---|---|

| XA6SLX100-2FGG484I | IC FPGA SPARTAN 6 484FGGBGA |

| 25LC640T-E/SN | IC EEPROM 64KBIT 2MHZ 8SOIC |

| SST25VF020B-80-4C-SAE-T | IC FLASH SER 2MB 80MHZ SPI 8SOIC |

| XC6SLX100-N3FGG484I | IC FPGA SPARTAN-6 484FPGA |

| SST25LF020A-33-4C-SAE | IC FLASH SER 2MB 33HZ SPI 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2S400E-6FGG456I | 制造商:Xilinx 功能描述:FPGA SPARTAN-IIE 400K GATES 10800 CELLS 357MHZ 1.8V 456FBGA - Trays |

| XC2S400E-6FGG676C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6FGG676I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6FT256C | 功能描述:IC SPARTAN-IIE FPGA 400K 256FTBG RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC2S400E-6FT256I | 制造商:Xilinx 功能描述:FPGA SPARTAN-IIE 400K GATES 10800 CELLS 357MHZ 1.8V 256FTBGA - Trays |

发布紧急采购,3分钟左右您将得到回复。