- 您现在的位置:买卖IC网 > PDF目录300163 > ZL30108LDG1 (XILINX INC) ATM/SONET/SDH SUPPORT CIRCUIT, QCC32 PDF资料下载

参数资料

| 型号: | ZL30108LDG1 |

| 厂商: | XILINX INC |

| 元件分类: | 数字传输电路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, QCC32 |

| 封装: | 5 X 5 MM, 0.90 MM HEIGHT, 0.50 MM PITCH, LEAD FREE, MO-220, QFN-32 |

| 文件页数: | 1/57页 |

| 文件大小: | 691K |

| 代理商: | ZL30108LDG1 |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2004-2009, Zarlink Semiconductor Inc. All Rights Reserved.

Features

Supports output wander and jitter generation

specifications for GR-253-CORE OC-3 and G.813

STM-1 SONET/SDH interfaces

Accepts two input references and synchronizes to

any combination of 2 kHz, 8 kHz, 1.544 MHz,

2.048 MHz, 8.192 MHz, 16.384 MHz or 19.44 MHz

inputs

Provides a 19.44 MHz (SONET/SDH) clock output

Provides an 8 kHz framing pulse and a 2 kHz

multi-frame pulse

Provides automatic entry into Holdover and return

from Holdover

Hitless reference switching between any

combination of valid input reference frequencies

Provides lock and accurate reference fail

indication

Loop filter bandwidth of 29 Hz or 14 Hz

Less than 24 psrms intrinsic jitter on the 19.44 MHz

output clock, compliant with GR-253-CORE OC-3

and G.813 STM-1 specifications

Less than 0.5 nspp intrinsic jitter on output frame

pulses

External master clock source: clock oscillator or

crystal

Simple hardware control interface

Applications

Line card synchronization for SONET/SDH

systems

Description

The ZL30108 SONET/SDH network interface digital

phase-locked

loop

(DPLL)

provides

timing

and

synchronization for SONET/SDH network interface

cards.

The ZL30108 generates a SONET/SDH clock and

framing signals that are phase locked to one of two

backplane or network references. It helps ensure

system reliability by monitoring its references for

frequency accuracy and stability and by maintaining

tight phase alignment between the input reference

clock and clock outputs.

The

ZL30108

output

clock’s

wander

and

jitter

generation are compliant with GR-253-CORE OC-3

and G.813 STM-1 specifications.

May 2009

Ordering Information

ZL30108LDA

32 Pin QFN

Tubes, Bake & Drypack

ZL30108LDG1

32 Pin QFN*

Trays, Bake & Drypack

*Pb Free Matte Tin

-40

°C to +85°C

ZL30108

SONET/SDH

Network Interface DPLL

Data Sheet

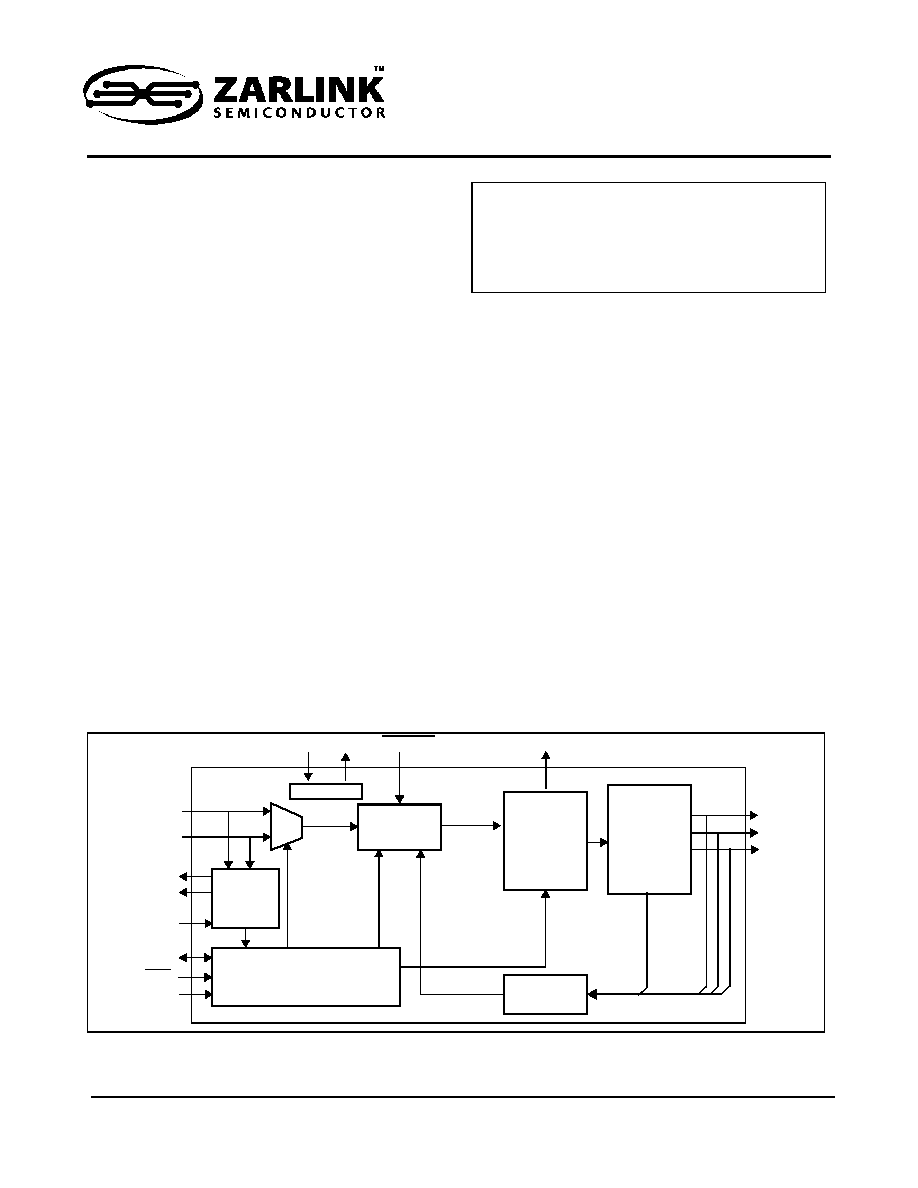

Figure 1 - Functional Block Diagram

Reference

Monitor

Mode

Control

Virtual

Reference

TIE

Corrector

Enable

State Machine

Frequency

Select

TIE

Corrector

Circuit

MODE_SEL

REF1

RST

REF_SEL

TIE_CLR

OSCo

OSCi

Master Clock

REF0

LOCK

REF_FAIL0

REF_FAIL1

DPLL

MUX

Frequency

Synthesizer

F8ko

C19o

F2ko

OOR_SEL

相关PDF资料 |

PDF描述 |

|---|---|

| ZL30316GKG2 | SPECIALTY TELECOM CIRCUIT, PBGA256 |

| ZL30316GKG | SPECIALTY TELECOM CIRCUIT, PBGA256 |

| ZL30402/QCC1 | ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 |

| ZL30402/QCG1 | ATM/SONET/SDH SUPPORT CIRCUIT, PQFP80 |

| ZL50112GAG2 | SPECIALTY TELECOM CIRCUIT, PBGA552 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL30109 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:DS1/E1 System Synchronizer with 19.44 MHz Output |

| ZL30109_05 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:DS1/E1 System Synchronizer with |

| ZL30109QDG | 制造商:Microsemi Corporation 功能描述: |

| ZL30109QDG1 | 制造商:Microsemi Corporation 功能描述:DS1/E1 System Synchronizer 64-Pin TQFP 制造商:Microsemi Corporation 功能描述:DS1/E1 SYS. SYNCH WITH 19.44MHZ 制造商:Microsemi Corporation 功能描述:DS1/E1 SYS SYNCHRONIZER 64TQFP - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SYNCHRONIZER DPLL 64TQFP 制造商:Microsemi Corporation 功能描述:IC SYNCHRONIZER DPLL 64TQFP |

| ZL30110 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:Telecom Rate Conversion DPLL |

发布紧急采购,3分钟左右您将得到回复。