- 您现在的位置:买卖IC网 > PDF目录278507 > ZPSD813F3V-20J 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 PDF资料下载

参数资料

| 型号: | ZPSD813F3V-20J |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 |

| 封装: | PLASTIC, LDCC-52 |

| 文件页数: | 68/132页 |

| 文件大小: | 513K |

| 代理商: | ZPSD813F3V-20J |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页当前第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页

PSD813F Family

Preliminary

36

The

PSD813F

Functional

Blocks

(cont.)

9.2 PLDs

The PLDs bring programmable logic functionality to the PSD813F. After specifying the

logic for the PLDs using the PSDabel tool in PSDsoft, the logic is programmed into the

device and available upon power-up.

The PSD813F contains two PLDs: the Decode PLD (DPLD), and the Complex PLD (CPLD).

The PLDs are briefly discussed in the next few paragraphs, and in more detail in sections

9.2.1 and 9.2.2. Figure 12 shows the configuration of the PLDs.

The DPLD performs address decoding for internal and external components, such as

memory, registers, and I/O port selects.

The CPLD can be used for logic functions, such as loadable counters and shift registers,

state machines, and encoding and decoding logic. These logic functions can be constructed

using the 16 Output Micro

Cells (OMCs), 24 Input MicroCells (IMCs), and the AND

array. The CPLD can also be used to generate external chip selects.

The AND array is used to form product terms. These product terms are specified using

PSDabel. An Input Bus consisting of 73 signals is connected to the PLDs. The signals are

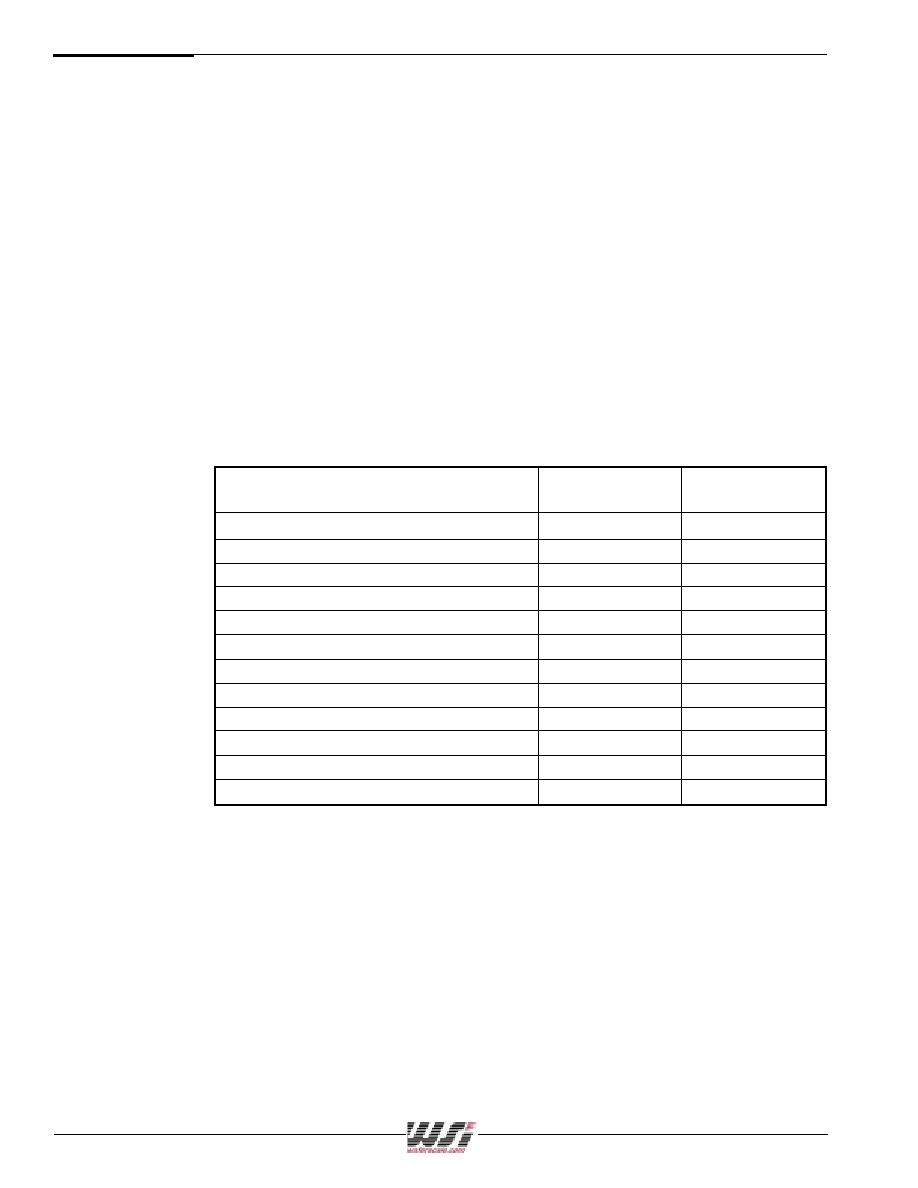

shown in Table 15.

Input Source

Input Name

Number

of Signals

MCU Address Bus

A[15:0]

*

16

MCU Control Signals

CNTL[2:0]

3

Reset

RST

1

Power Down

PDN

1

Port A Input Micro

Cells

PA[7-0]

8

Port B Input Micro

Cells

PB[7-0]

8

Port C Input Micro

Cells

PC[7-0]

8

Port D Inputs

PD[2:0]

3

Page Register

PGR(7:0)

8

Micro

Cell AB Feedback

MCELLAB.FB[7:0]

8

Micro

Cell BC Feedback

MCELLBC.FB[7:0]

8

EEPROM/Boot Flash Programming Status Bit

Rdy/Bsy

1

Table 15. DPLD and CPLD Inputs

NOTE: The address inputs are A[19:4] in 80C51XA mode.

The Turbo Bit in ZPSD813F

The PLDs in the ZPSD813F can minimize power consumption by switching off when inputs

remain unchanged for an extended time of about 70 ns. Setting the Turbo mode bit to off

(Bit 3 of the PMMR0 register) automatically places the PLDs into standby if no inputs

are changing. Turbo-off mode increases propagation delays while reducing power

consumption. Refer to the Power Management Unit section on how to set the Turbo Bit.

Additionally, five bits are available in the PMMR2 register to block MCU control signals from

entering the PLDs. This reduces power consumption and can be used only when these

MCU control signals are not used in PLD logic equations.

相关PDF资料 |

PDF描述 |

|---|---|

| ZDVG10A | 7 SEG NUMERIC DISPLAY, GREEN, 10.16 mm |

| ZMG75W | SINGLE COLOR LED, GREEN, 2.3 mm |

| ZMGUY62M-01 | DUAL COLOR LED |

| Z505 | INTERCONNECTION DEVICE |

| Z410 | INTERCONNECTION DEVICE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZPSD813F3V-A-15J | 制造商:WSI 功能描述: |

| ZPSD813F4-12JI | 制造商:WSI 功能描述: |

| ZPSD813F4-15J | 制造商:WSI 功能描述: 制造商:STMicroelectronics 功能描述:microcontroller peripheral devices 制造商:STMicroelectronics 功能描述:Flash in-system programmable microcontroller peripheral device |

| ZPSD813F4-90J | 制造商:WSI 功能描述: |

| ZPSD813F5-15J | 制造商:WSI 功能描述: |

发布紧急采购,3分钟左右您将得到回复。