- 您现在的位置:买卖IC网 > PDF目录1888 > 78Q8430-100IGT/F (Maxim Integrated Products)IC LAN MEDIA ACCESS CTLR 100LQFP PDF资料下载

参数资料

| 型号: | 78Q8430-100IGT/F |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 79/88页 |

| 文件大小: | 0K |

| 描述: | IC LAN MEDIA ACCESS CTLR 100LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 90 |

| 控制器类型: | 以太网控制器,MAC/PHY |

| 电源电压: | 3.3V |

| 电流 - 电源: | 230mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-LQFP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页当前第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

78Q8430 Data Sheet

DS_8430_001

80

Rev. 1.2

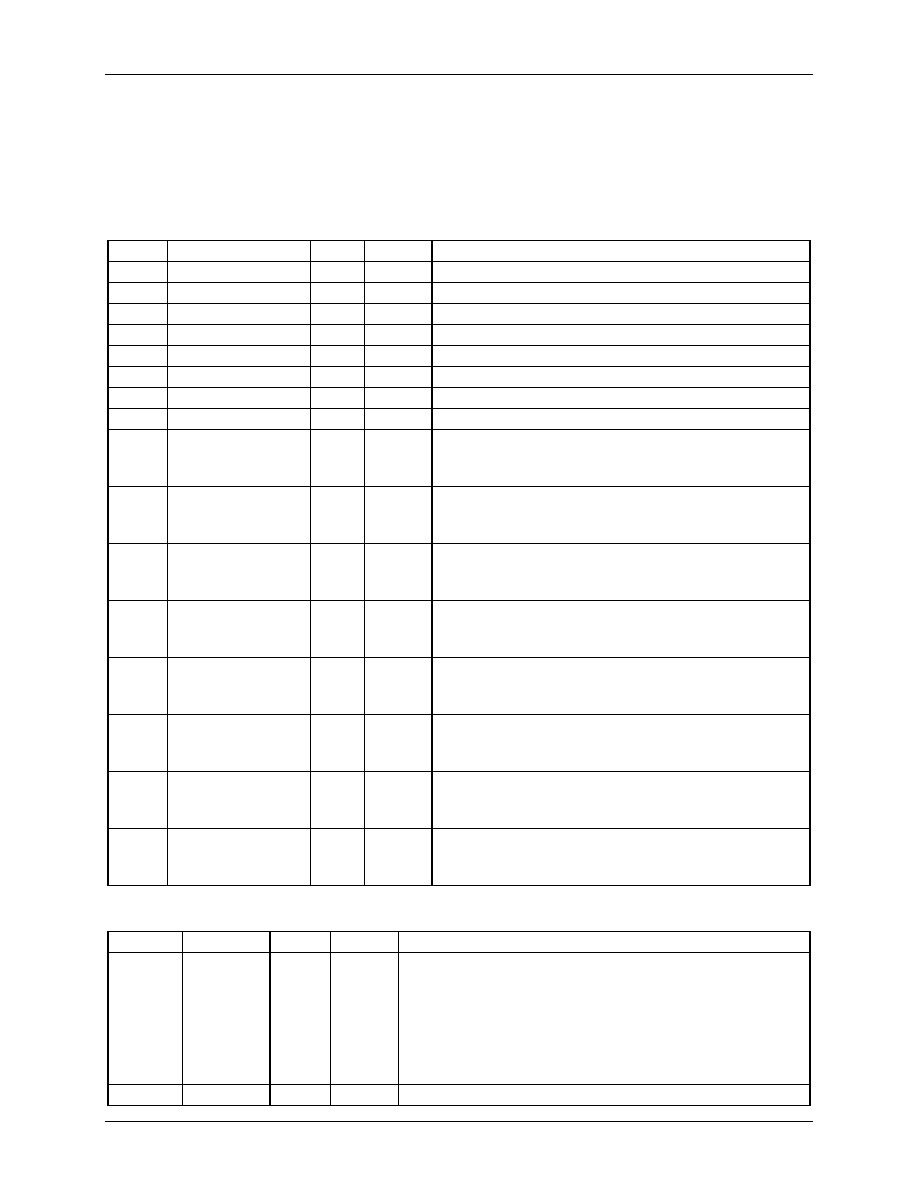

7.7.9

PHY Interrupt Control / Status Register – MR17

The Interrupt Control/Status Register provides the means for controlling and observing the events that

trigger an interrupt on the internal PHY interrupt signal. This register can also be used in a polling mode

via the MII Serial Interface as a means to observe key events within the PHY via one register address.

Bits 0 through 7 are status bits, which are each set to logic one based upon an event. These bits are

cleared after the register is read. Bits 8 through 15 of this register, when set to logic one, enable their

corresponding bit in the lower byte to signal an interrupt on the PHY interrupt signal.

Bits

Symbol

Type

Default Description

15

JABBER_IE

R/W

0

Jabber Interrupt Enable

14

RXER_IE

R/W

0

Receive Error Interrupt Enable

13

PRX_IE

R/W

0

Page Received Interrupt Enable

12

PDF_IE

R/W

0

Parallel Detect Fault Interrupt Enable

11

LP_ACK_IE

R/W

0

Link Partner Acknowledge Interrupt Enable

10

LS_CHANGE_IE

R/W

0

Link Status Change Interrupt Enable

9

RFAULT_IE

R/W

0

Remote Fault Interrupt Enable

8

ANEG-COMP_IE

R/W

0

Auto-Negotiation Complete Interrupt Enable

7

JAB_INT

RC

0

Jabber Interrupt

This bit is set high when a Jabber event is detected by

the 10Base-T circuitry.

6

RXER_INT

RC

0

Receive Error Interrupt

This bit is set high when the RX_ER signal transitions

high.

5

PRX_INT

RC

0

Page Received Interrupt

This bit is set high when a new page has been

received from the link partner during auto-negotiation.

4

PDF_INT

RC

0

Parallel Detect Fault Interrupt

This bit is set high by the auto-negotiation logic when a

parallel detect fault condition is indicated.

3

LP_ACK_INT

RC

0

Link Partner Acknowledge Interrupt

This bit is set high by the auto-negotiation logic when

FLP bursts are received with the acknowledge bit set.

2

LS_CHANGE_INT

RC

0

Link Status Change Interrupt

This bit is set when the link status transitions from an

OK status to a FAIL status, or vice versa.

1

RFAULT_INT

RC

0

Remote Fault Interrupt

This bit is set when a remote fault condition is

detected.

0

ANEG_COMP_INT

RC

0

Auto-Negotiation Complete Interrupt

This bit is set by the auto-negotiation logic upon

completion of auto-negotiation.

7.7.10 PHY Transceiver Control Register – MR19

Bit

Symbol

Type

Default Description

15:14

TXO[1:0]

R/W

01

Transmit Amplitude Selection

Sets the transmit output amplitude to account for transmit

transformer insertion loss.

00 = Gain set for 0.0dB of insertion loss

01 = Gain set for 0.4dB of insertion loss

10 = Gain set for 0.8dB of insertion loss

11 = Gain set for 1.2dB of insertion loss

13:0

RSVD

R/W

XXX

Reserved

相关PDF资料 |

PDF描述 |

|---|---|

| A1020B-1CQ84C | IC FPGA 2K GATES 84-CQFP COM |

| A1225A-1PQ100C | IC FPGA 2500 GATES 100-PQFP COM |

| A1440A-1VQG100I | IC FPGA 4K GATES 100-VQFP |

| A3P1000-1FGG484T | IC FPGA 1KB FLASH 1M 484-FBGA |

| A3PE1500-PQG208 | IC FPGA 444I/O 208PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 78Q8430-100IGTR/F | 功能描述:以太网 IC 10/100 Ethernet MAC & PHY RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| 78Q8430-128CGT/F | 制造商:Maxim Integrated Products 功能描述:Ethernet ICs 10/100 Ethernet MAC & PHY |

| 78Q8430-128CGTR/F | 制造商:Maxim Integrated Products 功能描述:Ethernet ICs 10/100 Ethernet MAC & PHY |

| 78Q8430-ARM9-EVM | 功能描述:EVALUATION MODULE 78Q8430 ARM9 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板 |

| 78Q8430EBST#DB | 功能描述:以太网开发工具 3-in-1 Silicon Delay Line RoHS:否 制造商:Micrel 产品:Evaluation Boards 类型:Ethernet Transceivers 工具用于评估:KSZ8873RLL 接口类型:RMII 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。